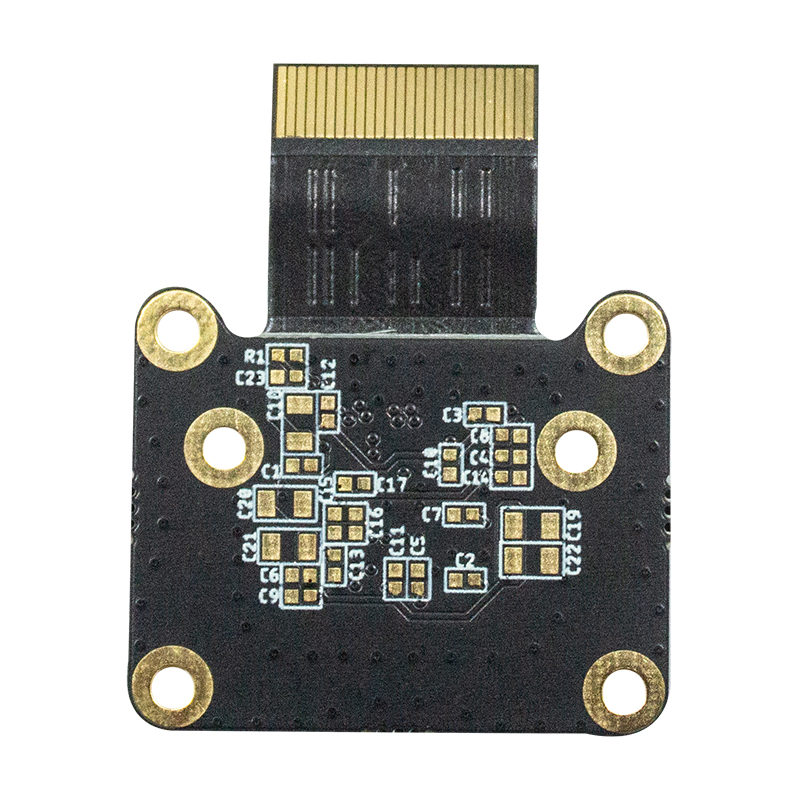

PCB (Printed Circuit Board) ass e wichtege Bestanddeel a modernen elektronesche Produkter, wat d'Verbindungen a Funktiounen vu verschiddenen elektronesche Komponenten erméiglecht. De PCB Produktiounsprozess beinhalt e puer Schlësselschrëtt, vun deenen ee Kupfer op de Substrat deposéiert. Dësen Artikel wäerte mir d'Methoden kucken fir Kupfer op PCB-Substrate während dem Produktiounsprozess ze deposéieren, an déi verschidden Techniken ze verdéiwen, sou wéi elektrolos Kupferplackéierung an Elektroplatéieren.

1.Electroless Kupferplack: Beschreiwung, chemesche Prozess, Virdeeler, Nodeeler a Beräicher vun der Applikatioun.

Fir ze verstoen wat elektrolos Kupferplack ass, ass et wichteg ze verstoen wéi et funktionnéiert. Am Géigesaz zu der Elektrodepositioun, déi op elektresche Stroum fir Metalldepositioun hänkt, ass elektrolos Kupferplack en autophoretesche Prozess. Et ëmfaasst déi kontrolléiert chemesch Reduktioun vu Kupferionen op engem Substrat, wat zu enger héich uniformer a konformer Kupferschicht resultéiert.

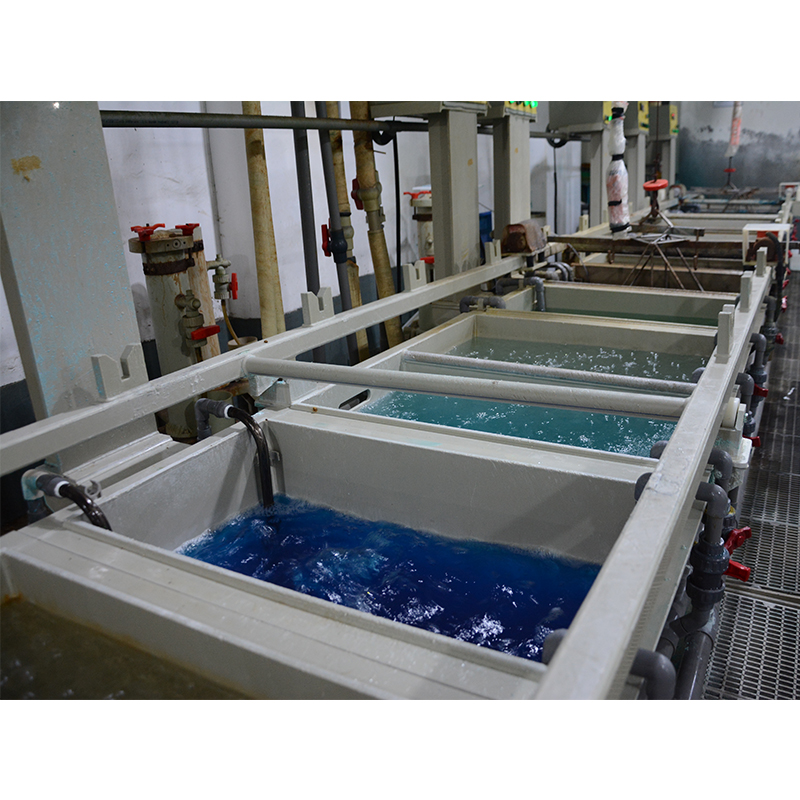

Botzen de Substrat:D'Substratoberfläche grëndlech botzen fir all Verschmotzung oder Oxide ze entfernen, déi Adhäsioun verhënneren. Aktivéierung: Eng Aktivéierungsléisung mat engem Edelmetallkatalysator wéi Palladium oder Platin gëtt benotzt fir den Elektroplatéierungsprozess unzefänken. Dës Léisung erliichtert Kupferablagerung op de Substrat.

Taucht an d'Platéierungsléisung:Taucht den aktivéierten Substrat an d'elektrolos Kupferplackléisung. D'Platéierungsléisung enthält Kupferionen, Reduktiounsmëttelen a verschidde Additive déi den Oflagerungsprozess kontrolléieren.

Electroplating Prozess:De Reduktiounsmëttel an der Elektroplatéierungsléisung reduzéiert chemesch Kupferionen an metallesch Kupferatome. Dës Atomer binden dann un déi aktivéiert Uewerfläch, a bilden eng kontinuéierlech an eenheetlech Schicht vu Kupfer.

Spülen an dréchen:Wann déi gewënschte Kupferdicke erreecht ass, gëtt de Substrat aus dem Plattbehälter geläscht a grëndlech gespullt fir all Rescht Chemikalien ze entfernen. Dréchent de placéierte Substrat virun der weiderer Veraarbechtung. Chemesche Kupferplackprozess De chemesche Prozess vun der elektroloser Kupferplackéierung beinhalt eng Redoxreaktioun tëscht Kupferionen a Reduzéierungsmëttel. Schlëssel Schrëtt am Prozess enthalen: Aktivéierung: D'Benotzung vun Edelmetall Katalysatoren wéi Palladium oder Platin fir d'Substratfläch ze aktivéieren. De Katalysator bitt déi néideg Plazen fir chemesch Bindung vu Kupferionen.

Reduktiounsmëttel:De Reduktiounsmëttel an der Plackéierungsléisung (normalerweis Formaldehyd oder Natriumhypophosphit) initiéiert d'Reduktiounsreaktioun. Dës Reagenz spenden Elektronen un Kupferionen, ëmgewandelt se an metallesch Kupferatome.

Autokatalytesch Reaktioun:D'Kupferatome produzéiert duerch d'Reduktiounsreaktioun reagéiere mam Katalysator op der Uewerfläch vum Substrat fir eng eenheetlech Kupferschicht ze bilden. D'Reaktioun geet weider ouni de Besoin fir en extern ugewandte Stroum, sou datt et "elektrolos Plackéierung" mécht.

Oflagerungsrate Kontroll:D'Zesummesetzung an d'Konzentratioun vun der Plattléisung, souwéi Prozessparameter wéi Temperatur a pH, gi suergfälteg kontrolléiert fir sécherzestellen datt d'Oflagerungsquote kontrolléiert an eenheetlech ass.

Virdeeler vun der elektrescher Kupferplackéierung Uniformitéit:Electroless Kupferplating huet eng exzellente Uniformitéit, déi eenheetlech Dicke a komplexe Formen a verstoppte Beräicher garantéiert. Konform Beschichtung: Dëse Prozess bitt eng konform Beschichtung déi gutt un geometresch onregelméisseg Substrate wéi PCBs hält. Gutt Adhäsioun: Elektrolos Kupferplack huet eng staark Adhäsioun op verschidde Substratmaterialien, dorënner Plastik, Keramik a Metaller. Selektiv Platéierung: Elektrolos Kupferplackéierung kann selektiv Kupfer op spezifesch Gebidder vun engem Substrat deposéieren mat Maskeringstechniken. Niddereg Käschte: Am Verglach mat anere Methoden ass elektrolos Kupferplating eng kosteneffektiv Optioun fir Kupfer op e Substrat ze deposéieren.

Nodeeler vun electroless Kupfer plating Méi lues Oflagerung Taux:Am Verglach mat Elektroplatéierungsmethoden, huet elektrolos Kupferplating typesch e méi luesen Oflagerungsquote, wat d'Gesamt Elektroplatéierungsprozesszäit verlängeren kann. Limitéiert Dicke: Elektrolos Kupferbeschichtung ass allgemeng gëeegent fir dënn Kupferschichten ze deposéieren an ass dofir manner gëeegent fir Uwendungen déi méi déck Oflagerungen erfuerderen. Komplexitéit: De Prozess erfuerdert virsiichteg Kontroll vu verschiddene Parameteren, dorënner Temperatur, pH a chemesche Konzentratioune, wat et méi komplex mécht fir ëmzesetzen wéi aner Elektroplatéierungsmethoden. Offallmanagement: Entsuergung vun Offallplackléisungen, déi gëfteg Schwéiermetalle enthalen, kënnen Ëmweltproblemer stellen an erfuerdert virsiichteg Handhabung.

Applikatioun Beräicher vun electroless Koffer plating PCB Fabrikatioun:Elektrolos Kupferplackung gëtt wäit an der Fabrikatioun vu gedréckte Circuitboards (PCBs) benotzt fir konduktiv Spuren ze bilden an duerch Lächer platéiert. Semiconductor Industrie: Spillt eng vital Roll an der Produktioun vun Hallefleitgeräter wéi Chipträger a Leadrahmen. Automobil- a Raumfaartindustrie: Elektrolos Kupferplack gëtt benotzt fir elektresch Stecker, Schalter an héich performant elektronesch Komponenten ze maachen. Dekorativ a funktionell Beschichtungen: Elektrolos Kupferbeschichtung kann benotzt ginn fir dekorativ Finishen op verschiddene Substrater ze kreéieren, souwéi fir Korrosiounsschutz a verbessert elektresch Konduktivitéit.

2.Kupferplack op PCB-Substrat

Kupferplating op PCB Substrater ass e kritesche Schrëtt am Gedréckte Circuit Board (PCB) Fabrikatiounsprozess. Kupfer gëtt allgemeng als Elektroplatéierungsmaterial benotzt wéinst senger exzellenter elektrescher Konduktivitéit an exzellenter Adhäsioun zum Substrat. De Kupferplackprozess beinhalt d'Depositioun vun enger dënnter Schicht Kupfer op der Uewerfläch vun engem PCB fir konduktiv Weeër fir elektresch Signaler ze kreéieren.

De Kupferplackprozess op PCB Substrate enthält normalerweis déi folgend Schrëtt: Surface Virbereedung:

De PCB-Substrat grëndlech botzen fir all Verschmotzung, Oxide oder Gëftstoffer ze entfernen, déi d'Adhäsioun behënneren kënnen an d'Qualitéit vun der Plackéierung beaflossen.

Virbereedung vun Elektrolyt:

Bereet eng Elektrolytléisung mat Kupfersulfat als Quell vu Kupferionen. Den Elektrolyt enthält och Additiven déi de Plackprozess kontrolléieren, sou wéi Niveléierungsmëttelen, Hellegkeeten a pH-Adjuster.

Elektrodepositioun:

Taucht de préparéierten PCB-Substrat an d'Elektrolytléisung a setzt Gläichstroum op. De PCB déngt als Kathodeverbindung, während eng Kupferanode och an der Léisung präsent ass. De Stroum bewierkt datt d'Kupferionen am Elektrolyt reduzéiert ginn an op d'PCB Uewerfläch deposéiert ginn.

Kontroll vun Plating Parameteren:

Verschidde Parameteren gi suergfälteg kontrolléiert wärend dem Plackprozess, inklusiv aktuell Dicht, Temperatur, pH, Rühren a Plackéierungszäit. Dës Parameteren hëllefen eng eenheetlech Oflagerung, Adhäsioun a gewënschte Dicke vun der Kupferschicht ze garantéieren.

Post-plating Behandlung:

Wann déi gewënschte Kupferdicke erreecht ass, gëtt de PCB aus dem Plackbad geläscht a gespullt fir all Rescht Elektrolytléisung ze läschen. Zousätzlech Post-Platéierungsbehandlungen, wéi Uewerflächenreinigung a Passivéierung, kënne gemaach ginn fir d'Qualitéit an d'Stabilitéit vun der Kupferplackschicht ze verbesseren.

Faktoren déi d'Qualitéit vun der Elektroplatéierung beaflossen:

Uewerfläch Virbereedung:

Richteg Botzen a Virbereedung vun der PCB Uewerfläch ass kritesch fir all Verschmotzung oder Oxidschichten ze läschen an eng gutt Adhäsioun vun der Kupferplack ze garantéieren. Zesummesetzung vun der Plating Léisung:

D'Zesummesetzung vun der Elektrolytléisung, och d'Konzentratioun vu Kupfersulfat an Zousatzstoffer, beaflosst d'Qualitéit vun der Plackéierung. D'Platéierungsbad Zesummesetzung soll suergfälteg kontrolléiert ginn fir déi gewënschte Plackeigenschaften z'erreechen.

Plating Parameteren:

D'Kontrolléiere vu Plackparameter wéi aktuell Dicht, Temperatur, pH, Rühren a Plattzäit ass néideg fir eenheetlech Oflagerung, Adhäsioun an Dicke vun der Kupferschicht ze garantéieren.

Substrat Material:

D'Typ an d'Qualitéit vum PCB-Substratmaterial beaflosst d'Haftung an d'Qualitéit vu Kupferplack. Verschidde Substratmaterialien kënnen Upassunge vum Plackprozess erfuerderen fir optimal Resultater.

Uewerfläch Rauhegkeet:

D'Uewerflächrauheet vum PCB-Substrat beaflosst d'Haftung an d'Qualitéit vun der Kupferplackschicht. Richteg Uewerfläch Virbereedung a Kontroll vun plating Parameteren hëllefen roughness-Zesummenhang Problemer minimiséieren

Virdeeler vum PCB Substrat Kupferplack:

Exzellent elektresch Konduktivitéit:

Kupfer ass bekannt fir seng héich elektresch Konduktivitéit, wat et eng ideal Wiel mécht fir PCB-Plackmaterialien. Dëst garantéiert effizient an zouverlässeg Leedung vun elektresche Signaler. Excellent Adhäsioun:

Kupfer weist exzellent Adhäsioun op verschidde Substrater, suergt fir eng staark a laang dauerhaft Verbindung tëscht der Beschichtung an dem Substrat.

Corrosion Resistenz:

Kupfer huet gutt Korrosiounsbeständegkeet, schützt ënnerierdesch PCB Komponenten a garantéiert laangfristeg Zouverlässegkeet. Solderbarkeet: Kupferplack bitt eng Uewerfläch gëeegent fir Löt, sou datt et einfach ass elektronesch Komponenten wärend der Montage ze verbannen.

Verbesserte Wärmevergëftung:

Kupfer ass e gudden thermesche Dirigent, wat effizient Wärmevergëftung vu PCBs erméiglecht. Dëst ass besonnesch wichteg fir héich Kraaft Uwendungen.

Aschränkungen an Erausfuerderunge vun der Kupfer Elektroplatéierung:

Dicke Kontroll:

Eng präzis Kontroll iwwer d'Kupferschichtdicke erreechen kann Erausfuerderung sinn, besonnesch a komplexe Beräicher oder enk Plazen op der PCB. Uniformitéit: Assuréieren eenheetlech Oflagerung vu Kupfer iwwer d'ganz Uewerfläch vun engem PCB, inklusiv ageschniddene Beräicher a feine Fonctiounen, kann schwéier sinn.

Käschten:

Elektroplating Kupfer ka méi deier sinn am Verglach mat anere Elektroplatéierungsmethoden wéinst de Käschte fir Panzerchemikalien, Ausrüstung an Ënnerhalt ze platzéieren.

Offallmanagement:

Entsuergung vu verbrauchte Plattléisungen a Behandlung vu Ofwaasser mat Kupferionen an aner Chemikalien erfuerdert entspriechend Offallmanagementpraktiken fir den Ëmweltimpakt ze minimiséieren.

Prozess Komplexitéit:

Electroplating Kupfer involvéiert verschidde Parameteren déi virsiichteg Kontroll erfuerderen, spezialiséiert Wëssen a komplexe Platéierungsopstellungen erfuerderen.

3.Vergleich tëscht elektrolosen Kupferplack an Elektroplating

Leeschtung a Qualitéit Differenzen:

Et gi verschidde Differenzen an der Leeschtung a Qualitéit tëscht elektroloser Kupferbeschichtung an Elektroplatéierung an de folgenden Aspekter:

Elektrolos Kupferplackéierung ass e chemesche Oflagerungsprozess deen keng extern Kraaftquell erfuerdert, wärend d'Elektroplätering involvéiert d'Benotzung vun Direktstroum fir eng Schicht Kupfer ze deposéieren. Dësen Ënnerscheed an Oflagerungsmechanismen kann zu Variatiounen an der Beschichtungsqualitéit féieren.

Electroless Kupferplating bitt allgemeng eng méi eenheetlech Oflagerung iwwer d'ganz Substratoberfläche, inklusiv ageschniddene Beräicher a fein Features. Dëst ass well d'Platéierung gläichméisseg op all Flächen geschitt onofhängeg vun hirer Orientéierung. Electroplating, op der anerer Säit, kann Schwieregkeeten hunn eng eenheetlech Oflagerung a komplexen oder schwéier z'erreechen Beräicher z'erreechen.

Elektrolos Kupferplating kann e méi héicht Aspekt Verhältnis (Verhältnis vu Feature Héicht bis Breet) erreechen wéi Elektroplating. Dëst mécht et gëeegent fir Uwendungen déi héich Aspekt Verhältnis Eegeschafte erfuerderen, sou wéi duerch Lächer an PCBs.

Elektrolos Kupferplating produzéiert allgemeng eng méi glatter, flaach Uewerfläch wéi Elektroplating.

Electroplating kann heiansdo zu ongläiche, rau oder ongëlteg Dépôten féieren wéinst Ännerungen an der aktueller Dicht a Badbedéngungen. D'Qualitéit vun der Bindung tëscht der Kupferplackschicht an dem Substrat ka variéieren tëscht elektrolose Kupferbeschichtung an Elektroplating.

Elektrolos Kupferplack bitt allgemeng besser Adhäsioun wéinst dem chemesche Bindungsmechanismus vum elektrolose Kupfer zum Substrat. Plating hänkt op mechanesch an elektrochemesch Bindung of, wat a verschiddene Fäll zu méi schwaache Bindungen resultéiere kann.

Käschte Verglach:

Chemesch Oflagerung vs.

Chemesch Käschten:

Elektrolos Kupferplating erfuerdert allgemeng méi deier Chemikalien am Verglach zum Elektroplating. D'Chemikalien, déi an der elektrescher Plackéierung benotzt ginn, wéi Reduzéierungsmëttelen a Stabilisatoren, si meeschtens méi spezialiséiert an deier.

Equipement Käschten:

Plating Unitéiten verlaangen méi komplex an deier Ausrüstung, dorënner Muecht Ëmgeréits, rectifiers an anodes. Elektrolos Kupferplacksystemer si relativ méi einfach a erfuerderen manner Komponenten.

Ënnerhalt Käschten:

Plating Ausrüstung kann periodesch Ënnerhalt, Kalibrierung an Ersatz vun Anoden oder aner Komponenten erfuerderen. Elektrolos Kupferplackéierungssystemer erfuerderen allgemeng manner heefeg Ënnerhalt an hunn manner allgemeng Ënnerhaltskäschte.

Verbrauch vu Plating Chemikalien:

Plating Systemer verbrauchen Plating Chemikalien zu engem méi héijen Taux wéinst der Benotzung vun elektresche Stroum. De chemesche Verbrauch vun elektrolosen Kupferplackéierungssystemer ass méi niddereg well d'Elektroplatingsreaktioun duerch eng chemesch Reaktioun geschitt.

Offallmanagement Käschten:

Electroplating generéiert zousätzlech Offall, dorënner verbrauchte Plattbäder a Spülenwasser kontaminéiert mat Metallionen, déi adequat Behandlung an Entsuergung erfuerderen. Dëst erhéicht d'Gesamtkäschte fir d'Platéierung. Electroless Koffer plating produzéiert manner Offall well et net op eng kontinuéierlech Fourniture vun Metal Ionen am plating Bad vertrauen.

Komplexitéiten an Erausfuerderunge vun Electroplating a Chemesch Oflagerung:

Electroplating erfuerdert virsiichteg Kontroll vu verschiddene Parameteren wéi aktuell Dicht, Temperatur, pH, Platéierungszäit a Rühr. Erreechen eenheetlech Oflagerung a gewënschte plating Charakteristiken kann Erausfuerderung ginn, virun allem an komplex Geometrien oder niddereg aktuell Beräicher. Optimisatioun vun plating Bad Zesummesetzung a Parameteren kann extensiv Experimenter an Expertise verlaangen.

Elektrolos Kupferplackéierung erfuerdert och Kontroll vu Parameteren wéi d'Reduktiounsmëttelkonzentratioun, Temperatur, pH a Platéierungszäit. Wéi och ëmmer, d'Kontroll vun dëse Parameteren ass allgemeng manner wichteg bei der elektroloser Platéierung wéi bei der Elektroplatéierung. D'Erreeche vun de gewënschten Plackeigenschaften, sou wéi Oflagerungsquote, Dicke an Adhäsioun, kann nach ëmmer Optimiséierung an Iwwerwaachung vum Plackprozess erfuerderen.

Bei der Elektropletterung an der elektroloser Kupferplackéierung kann d'Adhäsioun op verschidde Substratmaterialien eng gemeinsam Erausfuerderung sinn. Virbehandlung vun der Substratoberfläche fir Verschmotzungen ze entfernen an d'Adhäsioun ze förderen ass kritesch fir béid Prozesser.

Troubleshooting a Problemléisung bei der Elektropletterung oder elektroloser Kupferplating erfuerdert spezialiséiert Wëssen an Erfarung. Themen wéi Rauheet, ongläichméisseg Oflagerung, Voids, Bubbling, oder schlecht Adhäsioun kënne wärend béid Prozesser optrieden, an d'Wurzelursaach z'identifizéieren an d'Korrekturaktioun ze huelen kann Erausfuerderung sinn.

Ëmfang vun der Uwendung vun all Technologie:

Electroplating gëtt allgemeng an enger Vielfalt vun Industrien benotzt, dorënner Elektronik, Automobil, Raumfaart a Bijouen, déi präzis Dickekontrolle, qualitativ héichwäerteg Finish a gewënschte kierperlech Eegeschafte erfuerderen. Et gëtt wäit an dekorativen Finishen, Metallbeschichtungen, Korrosiounsschutz an Elektronesch Komponentfabrikatioun benotzt.

Elektrolos Kupferplackung gëtt haaptsächlech an der Elektronikindustrie benotzt, besonnesch an der Fabrikatioun vu gedréckte Circuitboards (PCBs). Et gëtt benotzt fir konduktiv Weeër, solderbar Flächen an Uewerflächefinishen op PCBs ze kreéieren. Elektrolos Kupferplackung gëtt och benotzt fir Plastik ze metalliséieren, Kupferverbindungen an Hallefleitverpackungen ze produzéieren, an aner Uwendungen déi eenheetlech a konform Kupferablagerung erfuerderen.

4.Kupferablagerungstechniken fir verschidde PCB-Typen

Single-sided PCB:

An eensäiteg PCBs gëtt Kupferablagerung normalerweis mat engem subtraktive Prozess duerchgefouert. De Substrat ass normalerweis aus engem net-leitend Material wéi FR-4 oder phenolescht Harz, mat enger dënnter Schicht Kupfer op enger Säit beschichtet. D'Kupferschicht déngt als de konduktive Wee fir de Circuit. De Prozess fänkt mat der Reinigung an der Virbereedung vun der Substratfläch un fir eng gutt Adhäsioun ze garantéieren. Als nächst ass d'Uwendung vun enger dënnter Schicht vu Photoresistmaterial, dat UV-Liicht duerch eng Fotomask ausgesat ass fir de Circuitmuster ze definéieren. Déi ausgesat Gebidder vum Resist ginn opléisbar a ginn duerno ofgewäsch, an déi ënnerierdesch Kupferschicht ausgesat. Déi ausgesat Kupferberäicher ginn dann mat engem Ätzmëttel wéi Ferrichlorid oder Ammoniumpersulfat geätzt. D'Ätzmëttel läscht selektiv ausgesat Kupfer, a léisst de gewënschte Circuitmuster. De Rescht Resist gëtt dann ofgerappt, a léisst d'Kupferspuren. Nom Ätzprozess kann d'PCB zousätzlech Uewerflächepräparatiounsschrëtt ënnerleien wéi Soldermaske, Écran Dréckerei, an Uwendung vu Schutzschichten fir Haltbarkeet a Schutz géint Ëmweltfaktoren ze garantéieren.

Duebelsäiteg PCB:

Eng duebelsäiteg PCB huet Kupferschichten op béide Säiten vum Substrat. De Prozess fir Kupfer op béide Säiten ze deposéieren implizéiert zousätzlech Schrëtt am Verglach mat eenzelne PCBs. De Prozess ass ähnlech wéi Single-sided PCB, ugefaange mat Botzen an Virbereedung vun der Substrat Uewerfläch. Eng Schicht vu Kupfer gëtt dann op béide Säiten vum Substrat deposéiert mat Hëllef vun elektrolosen Kupferplack oder Elektroplating. Electroplating gëtt typesch fir dëse Schrëtt benotzt well et eng besser Kontroll iwwer d'Dicke an d'Qualitéit vun der Kupferschicht erlaabt. Nodeems d'Kupferschicht deposéiert ass, gi béid Säite mat Photoresist beschichtet an de Circuitmuster gëtt duerch Beliichtungs- an Entwécklungsschrëtt definéiert ähnlech wéi déi fir eenzel Säit PCBs. Déi ausgesat Kupferberäicher ginn dann geätzt fir déi erfuerderlech Circuitspuren ze bilden. No Ätzen gëtt de Widderstand geläscht an de PCB geet duerch weider Veraarbechtungsschrëtt wéi d'Lötmaskapplikatioun an d'Uewerflächbehandlung fir d'Fabrikatioun vun engem doppelseitegen PCB ofzeschléissen.

Multilayer PCB:

Multilayer PCBs sinn aus multiple Schichten vu Kupfer an Isoléiermaterialien openee gestapelt. Kupferablagerung a Multilayer PCBs involvéiert verschidde Schrëtt fir konduktiv Weeër tëscht de Schichten ze kreéieren. De Prozess fänkt mat der Fabrikatioun vun den eenzelne PCB Schichten un, ähnlech wéi eenzel- oder zweesäiteg PCBs. All Schicht gëtt virbereet an e Photoresist gëtt benotzt fir de Circuitmuster ze definéieren, gefollegt vu Kupferablagerung iwwer Elektropletterung oder Elektrolos Kupferplating. No Oflagerung gëtt all Schicht mat engem Isoléiermaterial beschichtet (normalerweis epoxybaséiert Prepreg oder Harz) an dann zesumme gestapelt. D'Schichte ginn ausgeriicht mat Präzisiounsbueren a mechanesche Registréierungsmethoden fir eng korrekt Verbindung tëscht Schichten ze garantéieren. Wann d'Schichten ausgeriicht sinn, gi Vias erstallt andeems d'Lächer duerch d'Schichten op spezifesche Punkte gebrillt ginn, wou Interconnects erfuerderlech sinn. D'Vias ginn dann mat Kupfer platéiert mat der Elektropletterung oder elektroloser Kupferplating fir elektresch Verbindungen tëscht de Schichten ze kreéieren. De Prozess geet weider andeems d'Schichtstapelen, Bueren a Kupferplack Schrëtt widderhuelen bis all erfuerderlech Schichten a Verbindungen erstallt ginn. De leschte Schrëtt beinhalt d'Uewerflächenbehandlung, d'Lötmaskapplikatioun an aner Veraarbechtungsprozesser fir d'Fabrikatioun vum Multi-Layer PCB ofzeschléissen.

High Density Interconnect (HDI) PCB:

HDI PCB ass e Multi-Layer PCB entworf fir héich Dicht Circuit a klenge Form Faktor z'empfänken. Kupferablagerung an HDI PCBs involvéiert fortgeschratt Techniken fir fein Features a enk Pitch Designs z'erméiglechen. De Prozess fänkt un andeems verschidde ultradënn Schichten erstallt ginn, dacks Kärmaterial genannt. Dës Kären hunn dënn Kupferfolie op all Säit a sinn aus héich performant Harzmaterialien wéi BT (Bismaleimide Triazine) oder PTFE (Polytetrafluorethylene) gemaach. D'Kärmaterialien ginn gestapelt a laminéiert zesummen fir eng Multi-Layer Struktur ze kreéieren. Laserbohrung gëtt dann benotzt fir Mikrovias ze kreéieren, déi kleng Lächer sinn, déi d'Schichten verbannen. Microvias sinn typesch mat konduktiven Materialien wéi Kupfer oder konduktiv Epoxy gefüllt. Nodeems d'Mikrovias geformt sinn, ginn zousätzlech Schichten gestapelt a laminéiert. De sequentiellen Laminéierungs- a Laserbuerprozess gëtt widderholl fir verschidde gestapelte Schichten mat Mikrovia-Verbindungen ze kreéieren. Schlussendlech gëtt Kupfer op der Uewerfläch vum HDI PCB deposéiert mat Techniken wéi Elektropletterung oder elektrolos Kupferplackéierung. Wéinst de feine Featuren an d'héich Dicht Circuit vun HDI PCBs, gëtt Oflagerung suergfälteg kontrolléiert fir déi erfuerderlech Kupferschichtdicke a Qualitéit z'erreechen. De Prozess endet mat zousätzlech Uewerflächenbehandlung a Veraarbechtungsprozesser fir d'HDI PCB-Fabrikatioun ze kompletéieren, wat d'Lötmaskapplikatioun, d'Uewerflächefinanzéierungsapplikatioun an d'Tester enthalen kann.

Flexibel Circuit Board:

Flexibel PCBs, och bekannt als flex Circuits, sinn entwéckelt fir flexibel ze sinn a kënnen sech u verschidde Formen oder Béien während der Operatioun upassen. Kupferablagerung a flexiblen PCBs beinhalt spezifesch Techniken déi Flexibilitéit an Haltbarkeetfuerderunge entspriechen. Flexibel PCBs kënnen eensäiteg, duebelsäiteg oder méischichteg sinn, a Kupferablagerungstechniken variéieren op Basis vun Designfuerderunge. Allgemeng benotze flexibel PCBs méi dënn Kupferfolie am Verglach mat steife PCBs fir Flexibilitéit z'erreechen. Fir eensäiteg flexibel PCBs ass de Prozess ähnlech wéi eensäiteg steiwe PCBs, dat heescht, eng dënn Schicht vu Kupfer gëtt op de flexibele Substrat deposéiert mat der Hëllef vun elektroloser Kupferplack, Elektroplatéierung oder enger Kombinatioun vun deenen zwee. Fir doppelseiteg oder Multi-Layer flexibel PCBs, implizéiert de Prozess Kupfer op béide Säiten vum flexiblen Substrat ze deposéieren mat Hëllef vun elektrolosen Kupferplackéierung oder Elektroplatéieren. Berücksichtegt déi eenzegaarteg mechanesch Eegeschafte vu flexiblen Materialien, gëtt Oflagerung suergfälteg kontrolléiert fir eng gutt Adhäsioun a Flexibilitéit ze garantéieren. No der Kupferablagerung geet de flexibele PCB duerch zousätzlech Prozesser wéi Bueren, Circuitmusterung, an Uewerflächebehandlungsschrëtt fir déi erfuerderlech Circuit ze kreéieren an d'Fabrikatioun vum flexiblen PCB ofzeschléissen.

5.Fortschrëtter an Innovatiounen am Koffer Depositioun op PCBs

Déi lescht Technologieentwécklungen: Iwwer d'Joren ass d'Kupferablagerungstechnologie op PCBs weider entwéckelen a verbesseren, wat zu enger verstäerkter Leeschtung an Zouverlässegkeet resultéiert. E puer vun de leschten technologeschen Entwécklungen an der PCB Kupferablagerung enthalen:

Fortgeschratt Plating Technologie:

Nei Plating Technologien, wéi Pulsplating a Reverse Puls Plating, goufen entwéckelt fir méi fein a méi eenheetlech Kupferablagerung z'erreechen. Dës Technologien hëllefen Erausfuerderunge wéi Uewerfläch Rauhheet, Kärgréisst an Dicke Verdeelung ze iwwerwannen fir d'elektresch Leeschtung ze verbesseren.

Direkt Metalliséierung:

Traditionell PCB Fabrikatioun involvéiert verschidde Schrëtt fir konduktiv Weeër ze kreéieren, dorënner d'Depositioun vun enger Somschicht virum Kupferplack. D'Entwécklung vun direkten Metalliséierungsprozesser eliminéiert de Besoin fir eng separat Som Schicht, doduerch de Fabrikatiounsprozess vereinfacht, d'Käschte reduzéieren an d'Zouverlässegkeet verbesseren.

Microvia Technologie:

Microvias si kleng Lächer déi verschidde Schichten an engem Multilayer PCB verbannen. Fortschrëtter an der Mikrovia-Technologie wéi Laserbueren a Plasma Ätzen erméiglechen d'Schafung vu méi klengen, méi präzise Mikrovias, déi méi héich Dicht Circuits a verbessert Signalintegritéit erlaben. Surface Finish Innovation: Surface Finish ass kritesch fir Kupferspuren virun Oxidatioun ze schützen an d'Lötbarkeet ze bidden. Entwécklungen an Uewerflächenbehandlungstechnologien, wéi Immersion Silver (ImAg), Organic Solderability Preservative (OSP), an Electroless Nickel Immersion Gold (ENIG), bidden e bessere Korrosiounsschutz, verbesseren d'Lötbarkeet an erhéijen d'allgemeng Zouverlässegkeet.

Nanotechnologie a Kupferdepositioun: Nanotechnologie spillt eng wichteg Roll am Fortschrëtt vun der PCB Kupferablagerung. E puer Uwendunge vun der Nanotechnologie an der Kupferablagerung enthalen:

Nanopartikel-baséiert Plating:

Kupfer Nanopartikel kënnen an d'Platéierungsléisung agebaut ginn fir den Oflagerungsprozess ze verbesseren. Dës Nanopartikelen hëllefen d'Kupferhaftung, d'Korngréisst an d'Verdeelung ze verbesseren, doduerch d'Resistivitéit ze reduzéieren an d'elektresch Leeschtung ze verbesseren.

Nanostrukturéiert Conductive Materialien:

Nanostrukturéiert Materialien, wéi Kuelestoff Nanotubes a Graphen, kënnen an PCB-Substrate integréiert ginn oder als konduktiv Filler während der Oflagerung déngen. Dës Materialien hunn méi héich elektresch Konduktivitéit, mechanesch Kraaft an thermesch Eegeschaften, an doduerch d'Gesamtleistung vum PCB verbesseren.

Nanocoating:

Nanocoating kann op d'PCB Uewerfläch applizéiert ginn fir d'Uewerfläch glatt, solderability a corrosion Schutz ze verbesseren. Dës Beschichtungen ginn dacks aus Nanokomposite gemaach, déi e bessere Schutz géint Ëmweltfaktoren ubidden an d'Liewen vum PCB verlängeren.

Nanoscale interconnects:Nanoscale Interconnects, wéi Nanowires an Nanorods, ginn exploréiert fir méi héich Dicht Circuiten an PCBs z'erméiglechen. Dës Strukturen erliichteren d'Integratioun vu méi Circuiten an e méi klengt Gebitt, wat d'Entwécklung vu méi klengen, méi kompakten elektroneschen Apparater erlaabt.

Erausfuerderungen an zukünfteg Richtungen: Trotz bedeitende Fortschrëtter bleiwen e puer Erausfuerderungen a Méiglechkeete fir d'Kupferablagerung op PCBs weider ze verbesseren. E puer Schlëssel Erausfuerderungen an zukünfteg Richtungen enthalen:

Kupfer Fëllt an Héich Aspekt Verhältnis Strukturen:

Héich Aspekt Verhältnis Strukturen wéi Vias oder Microvias presentéieren Erausfuerderunge fir eenheetlech an zouverlässeg Kupferfill z'erreechen. Weider Fuerschung ass gebraucht fir fortgeschratt Platéierungstechniken oder alternativ Füllmethoden z'entwéckelen fir dës Erausfuerderungen ze iwwerwannen an eng korrekt Kupferablagerung an héije Aspektverhältnisser Strukturen ze garantéieren.

Kupfer Spuerbreet reduzéieren:

Wéi elektronesch Apparater méi kleng a méi kompakt ginn, wiisst de Besoin fir méi schmuel Kupferspuren weider. D'Erausfuerderung ass fir eenheetlech an zouverlässeg Kupferablagerung bannent dëse schmuele Spuren z'erreechen, fir konsequent elektresch Leeschtung an Zouverlässegkeet ze garantéieren.

Alternativ Dirigent Material:

Wärend Kupfer dat am meeschte benotzt Dirigentmaterial ass, ginn alternativ Materialien wéi Sëlwer, Aluminium a Kuelestoff Nanotubes exploréiert fir hir eenzegaarteg Eegeschaften a Leeschtungsvirdeeler. Zukünfteg Fuerschung kann sech op d'Entwécklung vun Oflagerungstechnike fir dës alternativ Dirigentmaterial konzentréieren fir Erausfuerderunge wéi Adhäsioun, Resistivitéit a Kompatibilitéit mat PCB-Fabrikatiounsprozesser ze iwwerwannen. ËmweltschutzFrëndschaftlech Prozesser:

D'PCB Industrie schafft konstant un ëmweltfrëndleche Prozesser. Zukünfteg Entwécklunge kënne sech op d'Reduktioun oder d'Eliminatioun vun der Notzung vu geféierleche Chemikalien während der Kupferablagerung konzentréieren, Energieverbrauch optimiséieren an Offallgeneratioun miniméieren fir den Ëmweltimpakt vun der PCB-Fabrikatioun ze reduzéieren.

Fortgeschratt Simulatioun a Modelléierung:

Simulatiouns- a Modellertechniken hëllefen d'Kupferablagerungsprozesser ze optimiséieren, d'Behuele vun Oflagerungsparameter virauszesoen an d'Genauegkeet an d'Effizienz vun der PCB-Fabrikatioun ze verbesseren. Zukünfteg Fortschrëtter kënnen d'Integratioun vun fortgeschratt Simulatiouns- a Modelléierungsinstrumenter an den Design- a Fabrikatiounsprozess involvéieren fir besser Kontroll an Optimiséierung z'erméiglechen.

6.Quality Assurance and Control of Copper Deposition for PCB Substrates

Wichtegkeet vun der Qualitéitssécherung: Qualitéitssécherung ass kritesch am Kupferdepositiounsprozess aus de folgende Grënn:

Produkt Zouverlässegkeet:

D'Kupferablagerung op der PCB bildt d'Basis fir elektresch Verbindungen. D'Qualitéit vu Kupferdepositioun assuréieren ass kritesch fir zouverlässeg a laang dauerhaft Leeschtung vun elektroneschen Apparater. Schlecht Kupferablagerung kann zu Verbindungsfehler, Signaldempung an allgemeng reduzéierter PCB Zouverlässegkeet féieren.

Elektresch Leeschtung:

D'Qualitéit vu Kupferplack beaflosst direkt d'elektresch Leeschtung vu PCB. Eenheetlech Kupferdicke a Verdeelung, glat Surface Finish, a richteg Adhäsioun si kritesch fir niddereg Resistenz, effizient Signaliwwerdroung a minimale Signalverloscht z'erreechen.

Käschten reduzéieren:

Qualitéitssécherung hëlleft d'Problemer fréi am Prozess z'identifizéieren an ze vermeiden, d'Noutwendegkeet ze reduzéieren fir defekt PCBs z'änneren oder ze verschrotten. Dëst kann Käschten spueren an allgemeng Fabrikatiounseffizienz verbesseren.

Client Zefriddenheet:

Héich Qualitéitsprodukter ubidden ass kritesch fir d'Zefriddenheet vun de Clienten an e gudde Ruff an der Industrie ze bauen. D'Clientë erwaarden zouverlässeg an haltbar Produkter, a Qualitéitssécherung garantéiert datt d'Kupferablagerung dës Erwaardungen entsprécht oder iwwerschreift.

Testen an Inspektiounsmethoden fir Kupferablagerung: Verschidde Test- an Inspektiounsmethoden gi benotzt fir d'Qualitéit vu Kupferablagerung op PCBs ze garantéieren. E puer allgemeng Methoden enthalen:

Visuell Inspektioun:

Visuell Inspektioun ass eng Basis a wichteg Method fir offensichtlech Uewerflächefehler z'entdecken wéi Kratzer, Dents oder Rauhegkeet. Dës Inspektioun kann manuell oder mat der Hëllef vun engem automateschen opteschen Inspektioun (AOI) System gemaach ginn.

Mikroskopie:

Mikroskopie mat Techniken wéi Scannen Elektronenmikroskopie (SEM) kann eng detailléiert Analyse vu Kupferablagerung ubidden. Et kann d'Uewerflächefinanz, d'Haftung an d'Uniformitéit vun der Kupferschicht suergfälteg iwwerpréiwen.

Röntgenanalyse:

Röntgenanalysetechniken, wéi Röntgenfluoreszenz (XRF) an Röntgendiffraktioun (XRD), gi benotzt fir d'Zesummesetzung, d'Dicke an d'Verdeelung vu Kupferablagerungen ze moossen. Dës Technike kënnen Gëftstoffer, elementar Zesummesetzung z'identifizéieren an all Inkonsistenz an der Kupferablagerung z'entdecken.

Elektresch Testen:

Maacht elektresch Testmethoden, inklusiv Resistenzmiessungen a Kontinuitéitstester, fir d'elektresch Leeschtung vu Kupferablagerungen ze evaluéieren. Dës Tester hëllefen sécherzestellen datt d'Kupferschicht déi erfuerderlech Konduktivitéit huet an datt et keng Ouverture oder Shorts am PCB gëtt.

Peel Kraaft Test:

De Peel Stäerkt Test moosst d'Verbindungsstäerkt tëscht der Kupferschicht an dem PCB Substrat. Et bestëmmt ob de Kupferdepot genuch Bindungsstäerkt huet fir normal Handhabung a PCB-Fabrikatiounsprozesser ze widderstoen.

Industrienormen a Reglementer: D'PCB Industrie follegt verschidde Industrienormen a Reglementer fir d'Qualitéit vu Kupferablagerung ze garantéieren. E puer wichteg Normen a Reglementer enthalen:

IPC-4552

Dëse Standard spezifizéiert d'Ufuerderunge fir electroless Nickel / Immersion Gold (ENIG) Uewerflächbehandlungen déi allgemeng op PCBs benotzt ginn. Et definéiert d'Mindest Golddicke, Néckeldicke an Uewerflächqualitéit fir zouverlässeg an haltbar ENIG Uewerflächbehandlungen.

IPC-A-600:

Den IPC-A-600 Standard liwwert PCB Akzeptanz Richtlinnen, dorënner Kupferplack Klassifikatioun Standarden, Uewerfläch Mängel an aner Qualitéit Standarden. Et déngt als Referenz fir visuell Inspektioun an Akzeptanzkriterien vu Kupferablagerung op PCBs. RoHS Direktiv:

D'Restriction of Hazardous Substances (RoHS) Direktiv beschränkt d'Benotzung vu bestëmmte geféierleche Substanzen an elektronesche Produkter, dorënner Bläi, Quecksilber a Kadmium. D'Konformitéit mat der RoHS-Direktiv garantéiert datt Kupferablagerungen op PCBs fräi vu schiedleche Substanzen sinn, wat se méi sécher a méi ëmweltfrëndlech mécht.

ISO 9001:

ISO 9001 ass den internationale Standard fir Qualitéitsmanagementsystemer. Etabléieren an Ëmsetzung vun engem ISO 9001-baséiert Qualitéitsmanagement System garantéiert datt entspriechend Prozesser a Kontrollen op der Plaz sinn fir konsequent Produkter ze liwweren déi de Client Ufuerderunge entspriechen, dorënner d'Qualitéit vu Kupferdepositioun op PCBs.

Gemeinsam Probleemer a Mängel reduzéieren: E puer allgemeng Probleemer a Mängel, déi während der Kupferdepositioun optrieden, enthalen:

Net genuch Adhäsioun:

Schlecht Adhäsioun vun der Kupferschicht zum Substrat kann zu Delaminatioun oder Peeling féieren. Richteg Uewerflächenreinigung, mechanesch Rauhung, an Adhäsiounsförderend Behandlungen kënnen hëllefen dëse Problem ze léisen.

Ongläiche Kupferdicke:

Ongläiche Kupferdicke kann onkonsequent Konduktivitéit verursaachen an d'Signaliwwerdroung behënneren. Optimiséierung vun der Plattéierungsparameter, mat Hëllef vu Puls oder ëmgedréint Pulsplating a suergt fir déi richteg Agitatioun kann hëllefe fir eenheetlech Kupferdicke z'erreechen.

Voids a Pinholes:

Voids a Pinholes an der Kupferschicht kënnen elektresch Verbindungen beschiedegen an de Risiko vu Korrosioun erhéijen. Richteg Kontroll vun Plating Parameteren a Gebrauch vun passenden Zousätz kann d'Optriede vun Void a pinholes minimiséieren.

Uewerfläch Rauhegkeet:

Exzessiv Uewerflächrauheet kann negativ Auswierkungen op PCB Leeschtung, d'Lötbarkeet an d'elektresch Integritéit beaflossen. Richteg Kontroll vu Kupferablagerungsparameter, Uewerfläch Virbehandlung a Postbehandlungsprozesser hëlleft eng glat Uewerfläch ze erreechen.

Fir dës Themen a Mängel ze reduzéieren, musse passend Prozesskontrollen ëmgesat ginn, reegelméisseg Inspektiounen an Tester musse gemaach ginn, an Industrienormen a Reglementer musse gefollegt ginn. Dëst garantéiert konsequent, zouverlässeg an héichqualitativ Kupferablagerung op der PCB. Zousätzlech, lafend Prozess Verbesserungen, Mataarbechter Training, a Feedback Mechanismen hëllefen Beräicher fir Verbesserung z'identifizéieren a Potential Problemer adresséieren ier se méi sérieux ginn.

Kupferablagerung op PCB-Substrat ass e kritesche Schrëtt am PCB-Fabrikatiounsprozess. Elektrolos Kupferablagerung an Elektroplatéieren sinn d'Haaptmethoden déi benotzt ginn, jidderee mat sengen eegene Virdeeler an Aschränkungen. Technologesch Fortschrëtter féieren weider Innovatiounen an der Kupferdepositioun ze féieren, an doduerch d'Performance an d'Zouverlässegkeet vun der PCB ze verbesseren.Qualitéitssécherung a Kontroll spillen eng vital Roll fir d'Produktioun vu qualitativ héichwäerteg PCBs ze garantéieren. Wéi d'Demande fir méi kleng, méi séier a méi zouverlässeg elektronesch Geräter weider eropgeet, sou geet d'Bedierfnes fir Präzisioun an Exzellenz an der Kupferablagerungstechnologie op PCB-Substraten. Bemierkung: D'Wuertzuel vum Artikel ass ongeféier 3.500 Wierder, awer bemierkt w.e.g. datt d'tatsächlech Wuertzuel liicht variéiere kann während dem Redaktiouns- a Korrekturlieseprozess.

Post Zäit: Sep-13-2023

Zréck