An dësem iwwergräifenden Artikel verdéiwen mir an d'Welt vu 4-Schicht PCB-Stackups, guidéieren Iech duerch déi bescht Designtechniken a Considératiounen.

Aféierung:

An der Welt vum PCB (gedréckte Circuit Verwaltungsrot) Design, ass et kritesch fir eng konsequent Leeschtung an zouverlässeg Funktionalitéit z'erreechen fir optimal Stackup ze erreechen. Fir déi ëmmer méi grouss Ufuerderunge vun modern elektronescher Ausrüstung z'erreechen, wéi méi séier Geschwindegkeet, méi héich Dicht a reduzéiert Signalinterferenz, ass e gutt geplangte 4-Schicht PCB-Stackup kritesch. Dësen Artikel déngt als ëmfaassend Guide fir Iech ze hëllefen d'Schlëssel Aspekter a Considératiounen ze verstoen, déi bei der Erreeche vun engem optimalen 4-Schicht PCB-Stack-up involvéiert sinn. Also, loosst eis an d'Welt vum PCB Stackup verdéiwen an d'Geheimnisser fir en erfollegräichen Design entdecken!

Inhalt:

1. Verstinn d'Basis vum 4-Schicht PCB Stacking:

- PCB Stackup: Wat ass et a firwat ass et wichteg?

- Schlëssel Considératiounen fir 4-Layer Stack Design.

- D'Wichtegkeet vun der korrekt Layer Arrangement.

- Signal- a Verdeelungsschichten: Rollen a Plazen.

- Faktoren déi d'Auswiel vun banneschten Kär a Prepreg Materialien beaflossen.

PCB Stackup:PCB-Stackup bezitt sech op d'Arrangement an d'Konfiguratioun vun de verschiddene Schichten an engem gedréckte Circuit Board. Et beinhalt d'Plaze vun konduktiven, isoléierenden a Signalverdeelungsschichten an enger spezifescher Uerdnung fir déi gewënscht elektresch Leeschtung a Funktionalitéit vum PCB z'erreechen. PCB Stackup ass wichteg well et d'Signalintegritéit, d'Muechtverdeelung, d'thermesch Gestioun an d'Gesamtleeschtung vum PCB bestëmmt.

Schlëssel Considératiounen fir 4-Layer Stack Design:

Wann Dir e 4-Schicht PCB-Stack-up designt, sinn e puer Schlësselbedéngungen:

Signal Integritéit:

D'Signalschichten no beieneen ze setzen, wärend d'Kraaft- a Buedemfliger niewendru behalen, verbessert d'Signalintegritéit andeems d'Impedanz tëscht Signalspuren a Referenzfliger reduzéiert gëtt.

Kraaft a Buedem Verdeelung:

Richteg Verdeelung a Plazéierung vu Kraaft- a Buedemfliger ass kritesch fir effektiv Kraaftverdeelung a Kaméidireduktioun. Et ass wichteg oppassen op d'Dicke an d'Distanz tëscht de Kraaft- a Buedemfliger fir d'Impedanz ze minimiséieren.

Thermesch Gestioun:

D'Plazéierung vun thermesche Vias an Hëtztbecher an d'Verdeelung vun thermesche Fligeren solle berücksichtegt ginn fir effektiv Wärmevergëftung ze garantéieren an Iwwerhëtzung ze vermeiden.

Komponentplacement a Routabilitéit:

Virsiichteg Berücksichtegung sollt d'Komponentplazéierung a Routing entscheeden fir eng optimal Signalrouting ze garantéieren an Signalinterferenz ze vermeiden.

D'Wichtegkeet vun der richteger Layer Arrangement:Layer Arrangement an engem PCB Stack ass kritesch fir d'Signalintegritéit z'erhalen, elektromagnetesch Interferenz (EMI) ze minimiséieren an d'Kraaftverdeelung ze managen. Richteg Layer Placement garantéiert kontrolléiert Impedanz, reduzéiert Crosstalk, a verbessert d'allgemeng Leeschtung vun der PCB Design.

Signal- a Verdeelungsschichten:D'Signaler ginn normalerweis op der ieweschter an ënnen Signalschichten geréckelt, während Kraaft- a Buedemfliger op der bannen sinn. D'Verdeelungsschicht handelt als Kraaft- a Buedemplang a bitt e Low-Impedanz-Wee fir Kraaft- a Buedemverbindungen, miniméiert Spannungsfall an EMI.

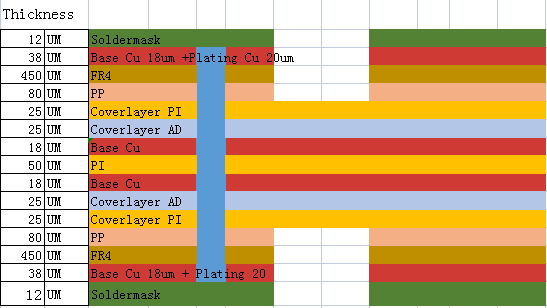

Faktoren déi Core a Prepreg Material Selektioun beaflossen:D'Wiel vu Kär- a Prepregmaterialien fir e PCB-Stackup hänkt vu Faktoren of wéi elektresch Leeschtungsufuerderungen, thermesch Gestiounsconsidératiounen, Fabrikatioun a Käschten. E puer wichteg Faktoren fir ze berücksichtegen enthalen dielektresch Konstant (Dk), Dissipatiounsfaktor (Df), Glasiwwergangstemperatur (Tg), Dicke a Kompatibilitéit mat Fabrikatiounsprozesser wéi Laminéierung a Buer. Virsiichteg Auswiel vun dëse Materialien garantéiert déi gewënscht elektresch a mechanesch Eegeschafte vum PCB.

2. Techniken fir optimal 4-Schicht PCB Stackup:

- Virsiichteg Komponentplacement a Spuerrouting fir effizient Kraaft a Signalintegritéit.

- D'Roll vun de Buedem- a Kraaftfliger fir Geräischer ze minimiséieren an d'Signalintegritéit ze maximéieren.

- Bestëmmt déi richteg Dicke an dielektresch Konstant vun all Schicht.

- Profitéiert vu kontrolléierter Impedanzrouting fir High-Speed-Designs.

- Thermesch Iwwerleeungen an thermesch Gestioun a Multilayer Stacks.

Dës Techniken hëllefen en optimalen 4-Schicht PCB-Stackup z'erreechen:

Virsiichteg Komponentplacement a Spuerrouting:Effizient Kraaft a Signalintegritéit kënnen duerch virsiichteg Komponentplacement a Spuerrouting erreecht ginn. Grupp verbonne Komponenten zesummen a suergen kuerz, direkt Verbindungen tëscht hinnen. Miniméiert d'Spuerlängt a vermeit d'Kräizung vu sensiblen Spuren. Benotzt richteg Abstand an haalt sensibel Signaler ewech vu Kaméidiquellen.

Buedem a Kraaftfliger:Buedem- a Kraaftfliger spillen eng vital Roll bei der Miniméierung vu Geräischer a maximal Signalintegritéit. Benotzt engagéierten Buedem- a Kraaftfliger fir e stabile Referenzplang ze bidden an elektromagnetesch Interferenz (EMI) ze reduzéieren. Sécherstellen adäquate Verbindungen zu dëse Fligeren engem nidderegen Impedanz Wee fir Retour aktuell ze erhalen.

Bestëmmt déi richteg Schichtdicke an Dielektresch Konstant:D'Dicke an dielektresch Konstant vun all Schicht am Stack beaflosst d'Signalverbreedung an d'Impedanzkontrolle. Bestëmmt de gewënschten Impedanzwäert a wielt déi entspriechend Dicke an dielektresch Konstant fir all Schicht entspriechend. Iwwerpréift d'PCB Design Richtlinnen a betruecht Signal Frequenz an Transmissioun Linn Ufuerderunge.

Kontrolléiert Impedanz Routing:Kontrolléiert Impedanz Routing ass kritesch fir High-Speed-Designs fir Signalreflexiounen ze minimiséieren, Signalintegritéit z'erhalen an Datefeeler ze vermeiden. Bestëmmt déi erfuerderlech Impedanzwäerter fir kritesch Signaler a benotzt kontrolléiert Impedanz Routing Techniken wéi Differentialpaar, Stripline oder Microstrip Routing, a kontrolléiert Impedanz Vias.

Thermesch Considératiounen a Gestioun:Thermesch Gestioun ass kritesch fir Multilayer PCB Stacks. Richteg Wärmevergëftung garantéiert datt d'Komponente bannent hiren Temperaturgrenzen funktionnéieren a potenziell Schued vermeit. Betruecht derbäi thermesch Vias fir Hëtzt op intern Buedemfliger oder thermesch Pads z'iwwerdroen, benotzt thermesch Vias bei héich Kraaftkomponenten, a kombinéiere mat Heizkierper oder Kupfer fir eng besser Hëtztverdeelung.

Andeems Dir dës Techniken ëmsetzt, kënnt Dir eng effizient Kraaftverdeelung garantéieren, Kaméidi minimiséieren, d'Signalintegritéit erhalen an d'thermesch Gestioun an engem 4-Schicht PCB-Stackup optimiséieren.

3. Design Considératiounen fir d'Fabrikatioun vun 4-Schicht PCB:

- Gläichgewiicht Fabrikatioun an Design Komplexitéit.

- Design fir Manufacturability (DFM) Best Practices.

- Via Typ an Layout Iwwerleeungen.

- Designregele fir Abstand, Spuerbreet a Spillraum.

- Schafft mam PCB Hiersteller fir optimal Stackup z'erreechen.

Balancéiere vun Fabrikatioun an Design Komplexitéit:Wann Dir e 4-Schicht PCB designt, ass et wichteg e Gläichgewiicht tëscht Designkomplexitéit a Fabrikatiounsliicht ze treffen. Komplex Designen kënnen d'Fabrikatiounskäschte a potenziell Feeler erhéijen. Vereinfachung vun Designen andeems d'Komponentplazéierung optiméiert, d'Signalrouting organiséiert, a standardiséierte Designregele benotze kënnen d'Fabrikabilitéit verbesseren.

Design for Manufacturability (DFM) Best Practices:Integréiert DFM Considératiounen an Designen fir effizient a Feelerfräi Fabrikatioun ze garantéieren. Dëst beinhalt d'folgend Industrie-Standard Designregelen, d'Auswiel vun passenden Materialien an Dicken, berécksiichtegt Fabrikatiounsbeschränkungen wéi minimal Spuerbreet an Abstand, a vermeit komplex Formen oder Features déi d'Komplexitéit vun der Fabrikatioun bäidroe kënnen.

Duerch Typ a Layout Iwwerleeungen:D'Auswiel vun der richteger Via-Typ a säi Layout ass kritesch fir e 4-Schicht PCB. Vias, blann Vias, a begruewe Vias hunn all seng Virdeeler an Aschränkungen. Betruecht virsiichteg hir Notzung baséiert op Design Komplexitéit an Dicht, a suergen adäquate Spillraum an Abstand ronderëm vias Signal Stéierungen an elektresch Kopplung ze vermeiden.

Designregele fir Abstand, Trace Breet a Clearance:Follegt d'recommandéiert Designregele fir Abstand, Spuerbreet a Spillraum, déi vum PCB Hiersteller zur Verfügung gestallt gëtt. Dës Regele garantéieren datt den Design ouni Probleemer fabrizéiert ka ginn, sou wéi elektresch Shorts oder Signaldegradatioun. Erhalen adäquate Distanz tëscht Spuren a Komponente, erhalen adäquate Spillraum an héich-Volt Beräicher, an der adäquate Spuer Breet fir déi gewënschte aktuell Droen Muecht sinn all wichteg Considératiounen.

Schafft mam PCB Hiersteller fir optimal Stackup:Schafft mam PCB Hiersteller fir den optimalen Stackup fir e 4-Layer PCB ze bestëmmen. Faktore fir ze berücksichtegen enthalen Kupferschichten, dielektrescht Materialauswiel a Plazéierung, gewënschte Impedanzkontroll, a Signalintegritéit Ufuerderunge. Andeems Dir enk mat Hiersteller schafft, kënnt Dir suergen datt PCB Designs mat hire Fäegkeeten a Fabrikatiounsprozesser ausgeriicht sinn, wat zu enger méi effizienter a kosteneffektiver Produktioun resultéiert.

Insgesamt erfuerdert den Design vun engem 4-Schicht PCB e grëndleche Verständnis vun der Fabrikatioun, d'Anhale vun DFM Best Practices, suergfälteg Iwwerleeung iwwer Typ a Layout, Anhale vun Designregelen, an Zesummenaarbecht mam PCB Hiersteller fir en optimalen Stackup z'erreechen. Andeems Dir dës Faktoren berücksichtegt, kënnt Dir d'Fabrikatioun, d'Zouverlässegkeet an d'Performance vun Ärem PCB-Design verbesseren.

4. Virdeeler an Aschränkungen vum 4-Layer PCB Stackup:

- Verbessert d'Signalintegritéit, reduzéiert Geräischer a miniméiert EMI Effekter.

- Verbessert Fäegkeet fir High-Speed-Designen ëmzesetzen.

- Plazspuerend Virdeel vu kompakter Elektronik.

- Potenziell Aschränkungen an Erausfuerderunge fir e 4-Schicht Stack ëmzesetzen.

Virdeeler vum 4-Schicht PCB Stackup:

Verbesserte Signal Integritéit:

Zousätzlech Buedem- a Kraaftfliger am 4-Schicht Stack hëllefen Signalgeräischer ze reduzéieren an eng besser Signalintegritéit fir High-Speed-Designs ze garantéieren. D'Buedemfläch handelt als zouverléisseg Referenzfläch, reduzéiert d'Signaliwwersprooch a verbessert d'Impedanzkontrolle.

Reduzéiert Kaméidi an EMI Impakt:

D'Präsenz vu Buedem- a Kraaftfliger am 4-Schicht-Stack hëlleft d'elektromagnetesch Interferenz (EMI) ze minimiséieren andeems se Schirmung a verbesserte Signalergrond liwweren. Dëst stellt eng besser Kaméidi Reduktioun a garantéiert méi kloer Signal Transmissioun.

Méi Fäegkeet fir High-Speed-Designen ëmzesetzen:

Mat zousätzlech Schichten hunn Designer méi Routingoptiounen. Dëst erméiglecht komplex High-Speed-Designer mat kontrolléierten Impedanzfuerderungen, reduzéiert Signaldempung an erreechen zouverlässeg Leeschtung bei méi héije Frequenzen.

Plazspuerend Virdeel:

4-Schicht Stacking erlaabt e méi kompakten an effizienten Design. Et bitt zousätzlech Routingoptiounen a reduzéiert de Besoin fir extensiv Verbindung tëscht Komponenten, wat zu engem méi klenge Formfaktor fir den allgemenge elektronesche System resultéiert. Dëst ass besonnesch gutt fir portable Elektronik oder dichtbevëlkerte PCBs.

Aschränkungen an Erausfuerderunge vun der Ëmsetzung vun engem 4-Schicht Stack:

Käschten:

Ëmsetzung vun engem 4-Schicht Stackup erhéicht d'Gesamtkäschte vum PCB am Verglach zu engem 2-Schicht Stackup. D'Käschte gi beaflosst vu Faktoren wéi d'Zuel vun de Schichten, Designkomplexitéit an erfuerderleche Fabrikatiounsprozess. Zousätzlech Schichten erfuerderen zousätzlech Materialien, méi präzis Fabrikatiounstechniken a fortgeschratt Routingfäegkeeten.

Design Komplexitéit:

Design vun engem 4-Schicht PCB erfuerdert méi virsiichteg Planung wéi en 2-Schicht PCB. Zousätzlech Schichten presentéieren Erausfuerderunge bei der Komponentplacement, Routing an iwwer Planung. D'Designer mussen d'Signalintegritéit, d'Impedanzkontroll a d'Kraaftverdeelung suergfälteg berücksichtegen, wat méi komplex an Zäitopwendeg ka sinn.

Produktiounsbeschränkungen:

D'Fabrikatioun vun 4-Schicht PCBs erfuerdert méi fortgeschratt Fabrikatiounsprozesser an Techniken. Hiersteller musse fäeg sinn d'Schichten präzis ausriichten an ze laminéieren, d'Dicke vun all Schicht ze kontrolléieren an eng korrekt Ausrichtung vu Bueraarbechten a Vias ze garantéieren. Net all PCB Hiersteller si kapabel fir effizient 4-Layer Boards ze produzéieren.

Kaméidi an Interferenz:

Wärend e 4-Schicht Stack-up hëlleft Geräischer an EMI ze reduzéieren, net genuch Design oder Layouttechniken kënnen nach ëmmer Kaméidi an Interferenzproblemer verursaachen. Ongerecht ausgefouert Layer Stacking oder net genuch Buedem kann zu ongewollt Kupplung a Signal Attenuatioun féieren. Dëst erfuerdert virsiichteg Planung an Iwwerleeung vum Design Layout a Buedemplangplaz.

Thermesch Gestioun:

D'Präsenz vun zousätzlech Schichten beaflosst d'Wärmevergëftung an d'thermesch Gestioun. Dicht Designen mat limitéierter Plaz tëscht Schichten kënnen zu enger verstäerkter thermescher Resistenz an der Hëtztopbau féieren. Dëst erfuerdert virsiichteg Iwwerleeung vum Komponent Layout, thermesch Vias, an allgemeng thermesch Design fir Iwwerhëtzungsproblemer ze vermeiden.

Et ass wichteg fir Designer hir Ufuerderungen suergfälteg ze evaluéieren, d'Virdeeler an d'Aschränkungen vun engem 4-Schicht PCB-Stackup berücksichtegen, fir eng informéiert Entscheedung iwwer dee beschten Stackup fir hire speziellen Design ze treffen.

Zesummefaassend,en optimalen 4-Schicht PCB-Stackup z'erreechen ass kritesch fir en zouverlässeg an héich performant elektroneschen Design ze garantéieren. Andeems Dir d'Grondlage versteet, Designtechniken berücksichtegt, a mat PCB Hiersteller kollaboréieren, kënnen Designer profitéieren vun effizienter Kraaftverdeelung, Signalintegritéit a reduzéierter EMI Effekter. Et muss drun erënnert ginn datt en erfollegräichen 4-Schicht Stack Design eng virsiichteg Approche an Iwwerleeung vu Komponentplacement, Routing, thermesch Gestioun an Fabrikatioun erfuerdert. Also huelt d'Wëssen an dësem Guide a fänkt Är Rees un fir dee beschten 4-Schicht PCB Stack fir Ären nächste Projet z'erreechen!

Post Zäit: Aug-18-2023

Zréck