16-Schicht PCBs bidden d'Komplexitéit an d'Flexibilitéit vun modernen elektroneschen Apparater. Kompetent Design a Selektioun vu Stacksequenzen an Interlayer Verbindungsmethoden si kritesch fir eng optimal Boardleistung z'erreechen. An dësem Artikel wäerte mir Considératiounen, Richtlinnen a beschten Praktiken entdecken fir Designer an Ingenieuren ze hëllefen effizient an zouverlässeg 16-Schicht Circuitboards ze kreéieren.

1.D'Grondlage vun 16 Layer PCBs Stacking Sequence verstoen

1.1 Definitioun an Zweck vun Stacking Uerdnung

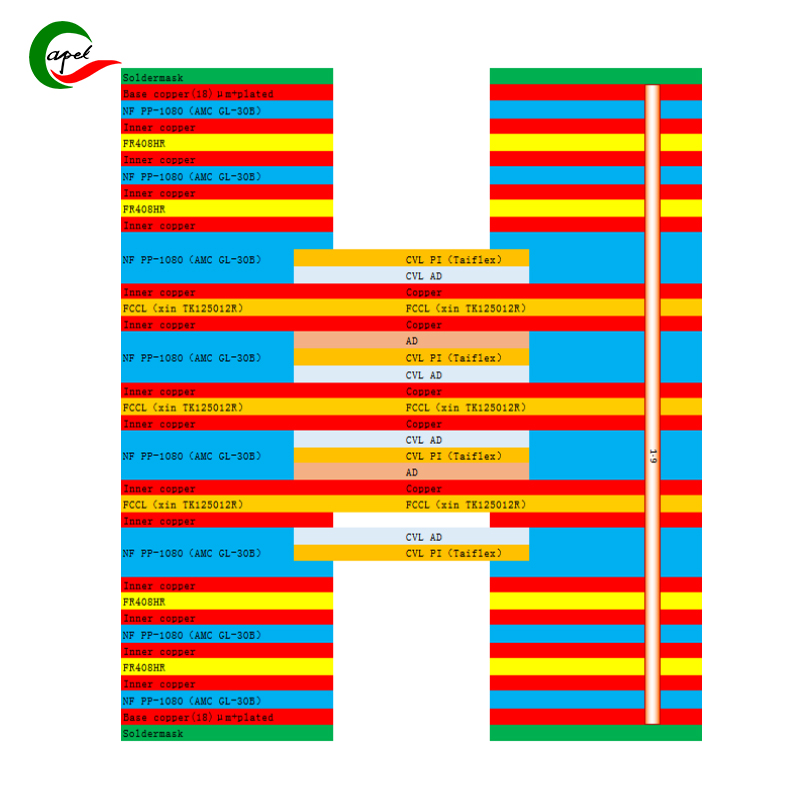

Stacking Sequenz bezitt sech op d'Arrangement an d'Uerdnung an deem Materialien wéi Kupfer an Isoléierschichten zesumme laminéiert sinn fir e Multi-Layer Circuit Board ze bilden. de Stack.

Den Haaptziel vun der Stacksequenz ass déi erfuerderlech elektresch a mechanesch Eegeschafte vum Board z'erreechen. Et spillt eng vital Roll bei der Bestëmmung vun der Impedanz vun engem Circuit Board, d'Signalintegritéit, d'Kraaftverdeelung, d'thermesch Gestioun, an d'Fabrikatiounsméiglechkeet. D'Stacking Sequenz beaflosst och d'Gesamtleistung, Zouverlässegkeet an Fabrikatioun vum Board.

1.2 Faktoren déi d'Stacksequenz Design beaflossen: Et gi verschidde Faktore fir ze berücksichtegen wann Dir d'Stacksequenz vun engem Design

16-Schicht PCB:

a) Elektresch Considératiounen:De Layout vun Signal, Kraaft, a Buedem Fligeren soll optimiséiert ginn adäquate Signal Integritéit ze garantéieren, Impedanz Kontroll, a Reduktioun vun elektromagnéiteschen Interferenz.

b) Thermesch Iwwerleeungen:D'Plazéierung vu Kraaft- a Buedemebenen an d'Inklusioun vun thermesche Vias hëllefen d'Hëtzt effektiv ze verdeelen an déi optimal Operatiounstemperatur vun der Komponent z'erhalen.

c) Fabrikatiounsbeschränkungen:D'Stacksequenz gewielt soll d'Fäegkeeten an d'Aschränkungen vum PCB-Fabrikatiounsprozess berücksichtegen, sou wéi d'Materialverfügbarkeet, d'Zuel vun de Schichten, d'Bohr Aspekt Verhältnis,an Ausriichtung Genauegkeet.

d) Käschteoptimiséierung:D'Auswiel vu Materialien, d'Zuel vun de Schichten, an d'Stack-up Komplexitéit sollte konsequent mam Projetsbudget sinn, wärend déi erfuerderlech Leeschtung an Zouverlässegkeet assuréiert.

1.3 Gemeinsam Aarte vu 16-Schichte Circuit Board Stacksequenzen: Et gi verschidde gemeinsame Stacksequenzen fir 16-Layer

PCB, jee no der gewënschter Leeschtung an Ufuerderunge. E puer allgemeng Beispiller enthalen:

a) Symmetresch Stacksequenz:Dës Sequenz beinhalt d'Signalschichten symmetresch tëscht Kraaft- a Buedemschichten ze placéieren fir eng gutt Signalintegritéit, minimale Crosstalk a equilibréiert Wärmevergëftung z'erreechen.

b) Sequentiell Stacksequenz:An dëser Sequenz sinn d'Signalschichten sequenziell tëscht der Kraaft- a Buedemschichten. Et bitt méi Kontroll iwwer d'Schichtarrangement an ass profitabel fir spezifesch Signalintegritéitsufuerderungen ze treffen.

c) Gemëscht Stack Uerdnung:Dëst beinhalt eng Kombinatioun vu symmetresche a sequentiellen Stackbestellungen. Et erlaabt Personnalisatioun an Optimiséierung vum Layup fir spezifesch Deeler vum Board.

d) Signalempfindlech Stacksequenz:Dës Sequenz placéiert sensibel Signalschichten méi no beim Buedemplang fir besser Geräischerimmunitéit an Isolatioun.

2.Schlëssel Iwwerleeungen fir 16 Layer PCB Stacking Sequence Selektioun:

2.1 Signalintegritéit a Kraaftintegritéit Iwwerleeungen:

D'Stacking Sequenz huet e wesentlechen Impakt op d'Signalintegritéit a Kraaftintegritéit vum Board. Richteg Plazéierung vu Signal- a Kraaft-/Buedemfliger ass kritesch fir de Risiko vu Signalverzerrung, Kaméidi an elektromagnetescher Amëschung ze minimiséieren. Schlëssel Considératiounen enthalen:

a) Signal Layer Placement:Héichgeschwindeg Signalschichten sollen no bei der Grondfläch plazéiert ginn fir e Low-Induktiounsretourwee ze bidden an d'Geräischkupplung ze minimiséieren. D'Signalschichten sollen och suergfälteg ausgeluecht ginn fir d'Signalskew an d'Längtmatchung ze minimiséieren.

b) Power Plane Verdeelung:D'Stacking Sequenz soll adäquate Muecht Fliger Verdeelung garantéieren Muecht Integritéit ze ënnerstëtzen. Genug Kraaft a Buedemplane solle strategesch plazéiert ginn fir Spannungsfäll, Impedanzdiskontinuitéiten a Geräischerkupplung ze minimiséieren.

c) Entkopplungskondensatoren:Richteg Plazéierung vun Ofkopplungskondensatoren ass kritesch fir adäquat Kraafttransfer ze garantéieren an Energieversuergungsrauschen ze minimiséieren. D'Stacking Sequenz soll d'Proximitéit an d'Proximitéit vun den Ofkupplungskondensatoren un d'Kraaft- a Buedemfliger ubidden.

2.2 Wärmemanagement a Wärmevergëftung:

Effizient thermesch Gestioun ass kritesch fir Circuitboard Zouverlässegkeet an Leeschtung ze garantéieren. D'Stacking Sequenz soll d'korrekt Plazéierung vu Kraaft- a Buedemfliger, thermesch Vias an aner Killmechanismen berücksichtegen. Wichteg Iwwerleeungen enthalen:

a) Power Plane Distribution:Adäquate Verdeelung vun Muecht a Buedem Fligeren ganze Stack hëlleft direkt Hëtzt ewech vun sensibel Komponente a garantéiert eenheetlech Temperatur Verdeelung iwwer de Comité.

b) Thermesch Vias:D'Stacking Sequenz soll effektiv thermesch iwwer Placement erlaben fir d'Wärmevergëftung vun der bannenzeger Schicht op d'äusseren Schicht oder d'Hëtzt ënnerzegoen. Dëst hëlleft lokaliséiert Hotspots ze vermeiden a garantéiert effizient Wärmevergëftung.

c) Bestanddeelplacement:Stacking Sequenz sollt d'Arrangement an d'Proximitéit vun den Heizkomponenten berücksichtegen fir Iwwerhëtzung ze vermeiden. Richteg Ausrichtung vu Komponenten mat Killmechanismus wéi Heizkierper oder Fans sollten och berücksichtegt ginn.

2.3 Fabrikatiounsbeschränkungen a Käschteoptimiséierung:

D'Stacking Sequenz muss d'Produktiounsbeschränkungen an d'Käschteoptimiséierung berücksichtegen, well se eng wichteg Roll an der Machbarkeet an der Bezuelbarkeet vum Board spillen. Iwwerleeungen enthalen:

a) Material Disponibilitéit:D'Stacksequenz gewielt soll konsequent mat der Disponibilitéit vu Materialien an hirer Kompatibilitéit mam gewielte PCB-Fabrikatiounsprozess sinn.

b) Zuel vu Schichten a Komplexitéit:D'Stacking Sequenz soll bannent de Contrainten vum gewielte PCB Fabrikatiounsprozess entworf ginn, berücksichtegt Faktore wéi d'Zuel vun de Schichten, d'Bohr Aspekt Verhältnis, an d'Ausrichtung Genauegkeet.

c) Käschteoptimiséierung:D'Stacking Sequenz soll d'Benotzung vu Materialien optimiséieren an d'Komplexitéit vun der Fabrikatioun reduzéieren ouni déi erfuerderlech Leeschtung an Zouverlässegkeet ze kompromittéieren. Et soll zielen d'Käschte verbonne mat Materialoffall, Prozesskomplexitéit a Montage ze minimiséieren.

2.4 Layer Ausrichtung a Signal Crosstalk:

D'Stackingssekvens soll d'Schichtausrichtungsprobleemer adresséieren an d'Signalcrosstalk minimiséieren, déi d'Signalintegritéit negativ beaflosse kënnen. Wichteg Iwwerleeungen enthalen:

a) Symmetresch Stacking:Symmetresch Stacking vun Signalschichten tëscht Kraaft- a Buedemschichten hëlleft d'Kupplung ze minimiséieren an d'Kräizung ze reduzéieren.

b) Differential Pair Routing:D'Stacking Sequenz sollt et erlaben datt d'Signalschichten richteg ausgeriicht ginn fir effizient Routing vun High-Speed-Differentialsignaler. Dëst hëlleft d'Signalintegritéit z'erhalen a Crosstalk ze minimiséieren.

c) Signal Trennung:D'Stacking Sequenz soll d'Trennung vu sensiblen Analog an Digital Signaler berücksichtegen fir Crosstalk an Interferenz ze reduzéieren.

2.5 Impedanz Kontroll an RF / Mikrowell Integratioun:

Fir RF / Mikrowell Uwendungen ass d'Stackungssequenz kritesch fir eng korrekt Impedanzkontroll an Integratioun z'erreechen. Schlëssel Iwwerleeungen enthalen:

a) Kontrolléiert Impedanz:D'Stacking Sequenz soll e kontrolléierten Impedanzdesign erlaben, Faktore berücksichtegt wéi Spuerbreet, dielektresch Dicke a Schichtarrangement. Dëst garantéiert eng korrekt Signalverbreedung an Impedanzmatchung fir RF / Mikrowell Signaler.

b) Signal Layer Placement:RF / Mikrowell Signaler solle strategesch no bei der äusserer Schicht plazéiert ginn fir Interferenz vun anere Signaler ze minimiséieren a besser Signalverbreedung ze bidden.

c) RF Schirmung:D'Stacking Sequenz sollt eng korrekt Plazéierung vu Buedem- a Schirmschichten enthalen fir RF / Mikrowell Signaler vu Stéierungen ze isoléieren an ze schützen.

3.Interlayer Connection Methoden

3.1 Duerch Lächer, Blannlächer a begruewe Lächer:

Vias gi wäit am gedréckte Circuit Board (PCB) Design benotzt als Mëttel fir verschidde Schichten ze verbannen. Si gi Lächer duerch all Schichten vum PCB gebohrt a si placéiert fir elektresch Kontinuitéit ze bidden. Duerch Lächer bidden eng staark elektresch Verbindung a si relativ einfach ze maachen an ze reparéieren. Wéi och ëmmer, si erfuerderen méi grouss Bohrbitsgréissten, déi wäertvoll Plaz op der PCB ophuelen a Routingoptiounen limitéieren.

Blann a begruewe Vias sinn alternativ interlayer Verbindungsmethoden déi Virdeeler an der Raumverbrauch a Routingflexibilitéit ubidden.

Blind Vias ginn aus der PCB Uewerfläch gebuert an enden an banneschten Schichten ouni duerch all Schichten ze goen. Si erlaben Verbindungen tëscht benachbarte Schichten wärend déif Schichten onaffektéiert loossen. Dëst erlaabt fir méi efficace Notzung vun Verwaltungsrot Plaz a reduzéiert d'Zuel vun Bueraarbechten Lächer. Begruewe Vias, op der anerer Säit, si Lächer déi komplett an den banneschten Schichten vum PCB zougemaach sinn an net op déi baussenzeg Schichten verlängeren. Si bidden Verbindungen tëscht banneschten Schichten ouni déi baussenzeg Schichten ze beaflossen. Begruewe vias hu méi Plaz-spueren Virdeeler wéi duerch-Lächer a blann vias well se keng Plaz an der baussenzegen Layer huelen.

D'Wiel vun duerch Lächer, blann vias, a begruewe vias hänkt op der spezifesch Ufuerderunge vun der PCB Design. Duerch Lächer ginn typesch a méi einfachen Designen benotzt oder wou Robustheet a Reparaturbarkeet primär Bedenken sinn. An High-Density Designs wou Plaz e kritesche Faktor ass, sou wéi Handheld Geräter, Smartphones a Laptops, blann a begruewe Vias si léiwer.

3.2 Micropore anHDI Technologie:

Microvias si klengen Duerchmiesser Lächer (normalerweis manner wéi 150 Mikron) déi High-Density Interlayer Verbindungen a PCBs ubidden. Si bidden bedeitend Virdeeler an der Miniaturiséierung, Signalintegritéit a Routingflexibilitéit.

Microvias kënnen an zwou Zorte opgedeelt ginn: Duerch-Lach Mikrovias a blann Mikrovias. Microvias ginn konstruéiert andeems d'Lächer vun der ieweschter Uewerfläch vun der PCB gebaut ginn an duerch all Schichten ausdehnen. Blind Mikrovias, wéi den Numm et scho seet, verlängeren nëmmen op spezifesch intern Schichten a penetréieren net all Schichten.

High-Density Interconnect (HDI) ass eng Technologie déi Mikrovias a fortgeschratt Fabrikatiounstechnike benotzt fir méi héich Circuitdicht a Leeschtung z'erreechen. HDI Technologie erlaabt d'Plazéierung vu méi klenge Komponenten a méi enk Routing, wat zu méi kleng Formfaktoren a méi héijer Signalintegritéit resultéiert. HDI Technologie bitt verschidde Virdeeler iwwer traditionell PCB Technologie a punkto Miniaturiséierung, verbesserte Signalverbreedung, reduzéierter Signalverzerrung a verstäerkter Funktionalitéit. Et erlaabt Multilayer Designs mat multiple Mikrovias, doduerch d'Verbindungslängt verkierzen an d'parasitär Kapazitéit an Induktioun reduzéieren.

HDI Technologie erlaabt och d'Benotzung vu fortgeschrattem Materialien wéi Héichfrequenz Laminate an dënn dielektresch Schichten, déi kritesch sinn fir RF / Mikrowellenapplikatiounen. Et bitt besser Impedanzkontrolle, reduzéiert Signalverloscht a garantéiert eng zouverlässeg Héichgeschwindegkeet Signaliwwerdroung.

3.3 Interlayer Verbindungsmaterialien a Prozesser:

D'Auswiel vun Interlayer Verbindungsmaterialien an Techniken ass kritesch fir eng gutt elektresch Leeschtung, mechanesch Zouverlässegkeet an Fabrikatioun vu PCBs ze garantéieren. E puer allgemeng benotzt interlayer Verbindungsmaterialien an Techniken sinn:

a) Kupfer:Kupfer gëtt wäit a konduktiv Schichten a Vias vu PCBs benotzt wéinst senger exzellenter Konduktivitéit a Lötbarkeet. Et ass normalerweis op d'Lach plated fir eng zouverlässeg elektresch Verbindung ze bidden.

b) Solderen:Soldertechniken, sou wéi Welleléisung oder Reflow-Lötung, ginn dacks benotzt fir elektresch Verbindungen tëscht duerch Lächer op PCBs an aner Komponenten ze maachen. Fëllt d'Lötpaste op d'Via an applizéiert Hëtzt fir d'Löt ze schmëlzen an eng zouverlässeg Verbindung ze bilden.

c) Electroplating:Elektroplating Techniken wéi elektrolos Kupferplackéierung oder elektrolytesch Kupfer gi benotzt fir Vias ze plackéieren fir d'Konduktivitéit ze verbesseren a gutt elektresch Verbindungen ze garantéieren.

d) Verbindung:Bindungstechniken, wéi Klebstoffverbindung oder Thermokompressiounsverbindung, gi benotzt fir Schichtenstrukturen zesummen ze verbannen an zouverlässeg Verbindungen ze kreéieren.

e) Dielektrescht Material:D'Wiel vun dielektrescht Material fir de PCB Stackup ass kritesch fir Interlayer Verbindungen. Héichfrequenz Laminate wéi FR-4 oder Rogers Laminate ginn dacks benotzt fir eng gutt Signalintegritéit ze garantéieren an de Signalverloscht ze minimiséieren.

3.4 Querschnitt Design a Bedeitung:

De Querschnittsdesign vum PCB-Stackup bestëmmt d'elektresch a mechanesch Eegeschafte vun de Verbindungen tëscht Schichten. Schlëssel Considératiounen fir Querschnitt Design enthalen:

a) Layer Arrangement:D'Arrangement vu Signal-, Kraaft- a Buedemfliger an engem PCB-Stackup beaflosst d'Signalintegritéit, d'Muechtintegritéit an d'elektromagnetesch Interferenz (EMI). Richteg Plazéierung an Ausriichtung vun Signalschichten mat Kraaft- a Buedemplanzen hëlleft Kaméidi Kopplung ze minimiséieren an niddereg Induktanzen zréck Weeër ze garantéieren.

b) Impedanz Kontroll:Querschnittsdesign soll kontrolléiert Impedanzfuerderunge berücksichtegen, besonnesch fir Héichgeschwindeg digital oder RF / Mikrowellsignaler. Dëst beinhalt eng passend Auswiel vun dielektresche Materialien an Dicken fir déi gewënscht charakteristesch Impedanz z'erreechen.

c) Wärmemanagement:De Querschnittsdesign soll effektiv Wärmevergëftung an thermesch Gestioun berücksichtegen. Richteg Plazéierung vu Kraaft- a Buedemfliger, thermesch Vias, a Komponenten mat Killmechanismus (wéi Heizkierper) hëllefen d'Hëtzt ze dissipéieren an optimal Operatiounstemperaturen z'erhalen.

d) Mechanesch Zouverlässegkeet:Sektioun Design soll mechanesch Zouverlässegkeet betruecht, virun allem an Uwendungen, datt zu thermesch Vëlo oder mechanesch Stress ënnerworf ginn. Richteg Auswiel vu Materialien, Bindungstechniken a Stackupkonfiguratioun hëllefen d'strukturell Integritéit an Haltbarkeet vum PCB ze garantéieren.

4.Design Richtlinnen fir 16-Layer PCB

4.1 Layer Allocation and Distribution:

Wann Dir e 16-Schicht Circuit Board designt, ass et wichteg d'Schichten virsiichteg ze verdeelen an ze verdeelen fir d'Performance an d'Signalintegritéit ze optimiséieren. Hei sinn e puer Richtlinnen fir Tierallokatioun

a Verdeelung:

Bestëmmt d'Zuel vun de Signalschichten erfuerderlech:

Bedenkt d'Komplexitéit vum Circuitdesign an d'Zuel vun de Signaler, déi routéiert musse ginn. Allokéiert genuch Signalschichten fir all erfuerderlech Signaler z'empfänken, adäquate Routingraum ze garantéieren an exzessiv ze vermeidenStau. Assignéiert Buedem- a Kraaftfliger:

Gitt op d'mannst zwou bannescht Schichten op Buedem- a Kraaftfliger. E Buedemplang hëlleft eng stabil Referenz fir Signaler ze bidden a miniméiert elektromagnetesch Interferenz (EMI). D'Kraaftfliger bitt e Low-Impedanz Kraaftverdeelungsnetz dat hëlleft Spannungsfäll ze minimiséieren.

Separat sensibel Signalschichten:

Ofhängeg vun der Applikatioun, kann et néideg sinn, sensibel oder High-Speed-Signalschichten vu Kaméidi oder High-Power Schichten ze trennen fir Interferenz a Crosstalk ze vermeiden. Dëst kann gemaach ginn andeems eng speziell Buedem- oder Kraaftfliger tëscht hinnen plazéiert oder Isolatiounsschichten benotzt.

Signalschichten gläichméisseg verdeelen:

Verdeelt d'Signalschichten gläichméisseg iwwer de Boardstack fir d'Kupplung tëscht ugrenzend Signaler ze minimiséieren an d'Signalintegritéit z'erhalen. Vermeiden d'Signalschichten niewenteneen am selwechte Stackberäich ze placéieren fir Interlayer Crosstalk ze minimiséieren.

Betruecht héich Frequenz Signaler:

Wann Ären Design Héichfrequenz Signaler enthält, betruecht d'Héichfrequenz Signalschichten méi no un de baussenzege Schichten ze placéieren fir d'Transmissiounslinn Effekter ze minimiséieren an d'Verbreedungsverzögerungen ze reduzéieren.

4.2 Routing a Signal Routing:

Routing a Signal Spuer Design si kritesch fir déi richteg Signalintegritéit ze garantéieren an d'Interferenz ze minimiséieren. Hei sinn e puer Richtlinnen fir Layout a Signalrouting op 16-Schicht Circuitboards:

Benotzt méi breet Spure fir High-Stroum Signaler:

Fir Signaler déi héich Stroum droen, wéi Kraaft a Buedemverbindungen, benotze méi breet Spure fir Resistenz a Spannungsfall ze minimiséieren.

Passend Impedanz fir High-Speed-Signaler:

Fir High-Speed-Signaler, suergt dofir datt d'Spureimpedanz mat der charakteristescher Impedanz vun der Iwwerdroungslinn entsprécht fir Reflexiounen a Signaldempung ze vermeiden. Benotzt kontrolléiert Impedanzdesigntechniken a korrekt Spuerbreetberechnungen.

Spuerlängen a Crossover Punkten minimiséieren:

Halt Spuerlängen esou kuerz wéi méiglech a reduzéiert d'Zuel vun de Crossover-Punkten fir parasitär Kapazitéit, Induktioun an Interferenz ze reduzéieren. Optimiséiert d'Placement vun de Komponenten a benotzt engagéiert Routingschichten fir laang, komplex Spuren ze vermeiden.

Separéiert High-Speed- a Low-Speed-Signaler:

Trennt High-Speed- a Low-Speed-Signaler fir den Impakt vum Geräischer op High-Speed-Signaler ze minimiséieren. Setzt High-Speed-Signaler op engagéierten Signalschichten an haalt se ewech vu High-Power oder Kaméidi Komponenten.

Benotzt Differentialpaar fir High-Speed-Signaler:

Fir Kaméidi ze minimiséieren an d'Signalintegritéit fir Héichgeschwindeg Differentialsignaler z'erhalen, benotzt Differentialpaar Routing Techniken. Halt d'Impedanz an d'Längt vun den Differentialpaaren passend fir Signalscheew a Crosstalk ze vermeiden.

4.3 Grondschicht a Kraaftschichtverdeelung:

Richteg Verdeelung vu Buedem- a Kraaftfliger ass kritesch fir eng gutt Kraaftintegritéit z'erreechen an elektromagnetesch Interferenz ze reduzéieren. Hei sinn e puer Richtlinnen fir Buedem- a Kraaftfliger Uerderen op 16-Schicht Circuitboards:

Allokéiert engagéiert Buedem- a Kraaftfliger:

Allokéiert op d'mannst zwou bannescht Schichten fir engagéierten Buedem- a Kraaftfliger. Dëst hëlleft Buedemschleifen ze minimiséieren, EMI ze reduzéieren an e Low-Impedanz Retour Wee fir Héichfrequenz Signaler ze bidden.

Separat digital an analog Buedemflächen:

Wann den Design digital an analog Sektiounen huet, ass et recommandéiert fir all Sektioun getrennte Buedemplanzen ze hunn. Dëst hëlleft Kaméidi Kopplung tëscht den digitalen an Analog Rubriken ze minimiséieren a Signal Integritéit verbessert.

Plaz Buedem- a Kraaftfliger no bei Signalfliger:

Plaz Buedem- a Kraaftfliger no bei de Signalfliger déi se fidderen fir d'Schleiffläch ze minimiséieren an de Geräischer Pickup ze reduzéieren.

Benotzt verschidde Vias fir Kraaftfliger:

Benotzt Multiple Vias fir Kraaftfliger ze verbannen fir d'Kraaft gläichméisseg ze verdeelen an d'Muechtfligerimpedanz ze reduzéieren. Dëst hëlleft d'Versuergungsspannungsfäll ze minimiséieren a verbessert d'Muechtintegritéit.

Vermeiden schmuel Hals a Kraaftfliger:

Vermeit schmuel Hals a Kraaftfliger, well se d'Stréimung verursaache kënnen an d'Resistenz erhéijen, wat zu Spannungsfäll a Kraaftfliger Ineffizienz resultéiert. Benotzen staark Verbindungen tëscht verschiddene Muecht Fliger Beräicher.

4.4 Thermesch Pad a via Placement:

Richteg Plazéierung vun thermesche Pads a Vias ass kritesch fir effektiv Hëtzt ze dissipéieren an d'Komponente vun Iwwerhëtzung ze vermeiden. Hei sinn e puer Richtlinnen fir thermesch Pad an iwwer Placement op 16-Schicht Circuit Boards:

Plaz thermesch Pad ënner Hëtzt generéierend Komponenten:

Identifizéieren déi Hëtzt-generéierend Komponent (wéi e Kraaftverstärker oder High-Power IC) a setzt den Thermalpad direkt drënner. Dës thermesch Pads bidden en direkten thermesche Wee fir Hëtzt op déi intern thermesch Schicht ze transferéieren.

Benotzt verschidde thermesch Vias fir Wärmevergëftung:

Benotzt verschidde thermesch Vias fir d'thermesch Schicht an d'äusser Schicht ze verbannen fir effizient Wärmevergëftung ze bidden. Dës Vias kënnen an engem verstoppte Muster ronderëm den thermesche Pad plazéiert ginn fir eng gläichméisseg Hëtztverdeelung z'erreechen.

Betruecht thermesch Impedanz a Layer Stackup:

Wann Design thermesch vias, betruecht der thermesch impedance vun der Verwaltungsrot Material an Layer stackup.Optimize via Gréisst an Abstand thermesch Resistenz ze minimiséieren an Hëtzt dissipation maximal.

4.5 Komponentplacement a Signalintegritéit:

Richteg Komponentplacement ass kritesch fir d'Signalintegritéit z'erhalen an d'Interferenz ze minimiséieren. Hei sinn e puer Richtlinnen fir Komponenten op engem 16-Schicht Circuit Board ze placéieren:

Gruppe verbonne Komponenten:

Grupp verbonne Komponenten déi Deel vum selwechte Subsystem sinn oder staark elektresch Interaktiounen hunn. Dëst reduzéiert d'Spuerlängt a miniméiert d'Signalattenuatioun.

Halt High-Speed-Komponenten no:

Setzt High-Speed-Komponenten, wéi Héichfrequenz Oszilléierer oder Mikrokontroller, no beienee fir Spuerlängen ze minimiséieren an déi richteg Signalintegritéit ze garantéieren.

Miniméiert d'Spuerlängt vu kriteschen Signaler:

Miniméiert d'Spuerlängt vu kritesche Signaler fir d'Verbreedungsverzögerung an d'Signalattenuatioun ze reduzéieren. Setzt dës Komponenten esou no wéi méiglech.

Separat sensibel Komponenten:

Trennt Kaméidi-sensibel Komponenten, wéi Analog Komponenten oder Low-Level Sensoren, vu High-Power oder Kaméidi Komponenten fir d'Interferenz ze minimiséieren an d'Signalintegritéit z'erhalen.

Bedenkt d'Entkupplungskondensatoren:

Setzt Ofkupplungskondensatoren esou no wéi méiglech un d'Kraaftpins vun all Komponent fir propper Kraaft ze bidden an Spannungsschwankungen ze minimiséieren. Dës Kondensatoren hëllefen d'Energieversuergung ze stabiliséieren an d'Geräischkupplung ze reduzéieren.

5.Simulatioun an Analyse Tools fir Stack-Up Design

5.1 3D Modelléierungs- a Simulatiounssoftware:

3D Modelléierungs- a Simulatiounssoftware ass e wichtegt Tool fir Stackup Design well et Designer erlaabt virtuell Representatioune vu PCB Stackups ze kreéieren. D'Software kann Schichten, Komponenten an hir kierperlech Interaktiounen visualiséieren. Andeems Dir de Stackup simuléiert, kënnen Designer potenziell Themen identifizéieren wéi Signal Crosstalk, EMI a mechanesch Aschränkungen. Et hëlleft och d'Arrangement vun de Komponenten z'iwwerpréiwen an de Gesamt PCB Design ze optimiséieren.

5.2 Signal Integritéit Analyse Tools:

Signal Integritéit Analyse Tools si kritesch fir d'elektresch Leeschtung vun PCB Stackups z'analyséieren an ze optimiséieren. Dës Tools benotze mathematesch Algorithmen fir Signalverhalen ze simuléieren an ze analyséieren, dorënner Impedanzkontrolle, Signalreflexiounen a Geräischerkupplung. Andeems Dir Simulatioun an Analyse ausféiert, kënnen Designer potenziell Signalintegritéitsprobleemer fréi am Designprozess identifizéieren an déi néideg Upassunge maachen fir zouverlässeg Signaliwwerdroung ze garantéieren.

5.3 Thermesch Analyse Tools:

Thermesch Analyse Tools spillen eng wichteg Roll am Stackup Design andeems se d'thermesch Gestioun vu PCBs analyséieren an optimiséieren. Dës Tools simuléieren d'Hëtztvergëftung an d'Temperaturverdeelung bannent all Schicht vum Stack. Andeems Dir d'Kraaftdissipatioun an d'Wärmetransferweeër präzis modelléiert, kënnen d'Designer Hot Spots identifizéieren, d'Placement vu Kupferschichten an thermesche Vias optimiséieren an eng korrekt Ofkillung vu kriteschen Komponenten garantéieren.

5.4 Design fir Fabrikatioun:

Design fir Fabrikatioun ass e wichtegen Aspekt vum Stackup Design. Et gi verschidde Software-Tools verfügbar déi hëllefe kënnen ze garantéieren datt de gewielte Stack-up effizient hiergestallt ka ginn. Dës Tools bidden Feedback iwwer d'Machbarkeet fir de gewënschten Stackup z'erreechen, berücksichtegt Faktore wéi Materialverfügbarkeet, Schichtdicke, Fabrikatiounsprozess, a Fabrikatiounskäschte. Si hëllefen Designer informéiert Entscheedungen ze treffen fir de Stacking ze optimiséieren fir d'Fabrikatioun ze vereinfachen, de Risiko vu Verspéidungen ze reduzéieren an d'Ausbezuelen ze erhéijen.

6.Step-by-Step Design Prozess fir 16-Layer PCBs

6.1 Éischt Ufuerderunge Sammlung:

An dësem Schrëtt, sammelen all déi néideg Ufuerderunge fir 16-Layer PCB Design. Verstinn d'Funktionalitéit vum PCB, erfuerderlech elektresch Leeschtung, mechanesch Aschränkungen an all spezifesch Design Richtlinnen oder Standarden déi gefollegt musse ginn.

6.2 Komponentallokatioun an Arrangement:

No Ufuerderunge, allokéieren Komponente op der PCB a bestëmmen hir Arrangement. Betruecht Faktore wéi Signal Integritéit, thermesch Considératiounen, a mechanesch Aschränkungen. Grupp Komponenten op Basis vun elektresche Charakteristiken a setzen se strategesch op de Bord fir d'Interferenz ze minimiséieren an d'Signalfloss ze optimiséieren.

6.3 Stack-up Design a Layer Verdeelung:

Bestëmmt de Stack-up Design fir de 16-Layer PCB. Bedenkt Faktore wéi dielektresch Konstant, thermesch Konduktivitéit a Käschten fir dat passend Material ze wielen. Assignéiert Signal, Kraaft a Buedemfliger no elektresch Ufuerderungen. Plaz Buedem- a Kraaftfliger symmetresch fir e equilibréierte Stack ze garantéieren an d'Signalintegritéit ze verbesseren.

6.4 Signal Routing a Routing Optimisatioun:

An dësem Schrëtt ginn Signalspuren tëscht Komponenten geréckelt fir eng korrekt Impedanzkontroll, Signalintegritéit ze garantéieren an d'Signaliwwerschwong ze minimiséieren. Optimiséiert Routing fir d'Längt vu kriteschen Signaler ze minimiséieren, sensibel Spuren ze vermeiden, an d'Trennung tëscht Héich- a Low-Speed-Signaler z'erhalen. Benotzt Differentialpaaren a kontrolléiert Impedanz Routing Techniken wann néideg.

6.5 Interlayer Verbindungen a via Placement:

Plan d'Placement vun Verbindung vias tëscht Schichten. Bestëmmen déi entspriechend via Typ, wéi duerch Lach oder blann Lach, baséiert op Layer Transitioune a Komponent Verbindungen. Optimiséiert iwwer Layout fir Signalreflexiounen, Impedanzdiskontinuitéiten ze minimiséieren, a souguer Verdeelung op der PCB z'erhalen.

6.6 Final Design Verifikatioun a Simulatioun:

Virun der Fabrikatioun ginn d'endgülteg Designverifizéierung a Simulatioune gemaach. Benotzt Simulatiounsinstrumenter fir PCB Designs fir Signalintegritéit, Kraaftintegritéit, thermesch Verhalen a Fabrikatioun ze analyséieren. Vergewëssert den Design géint initial Ufuerderungen a maacht déi néideg Upassunge fir d'Performance ze optimiséieren an d'Fabrikabilitéit ze garantéieren.

Kollaboréieren a kommunizéieren mat anere Akteuren wéi elektresch Ingenieuren, mechanesch Ingenieuren, a Fabrikatiounsteams am ganzen Designprozess fir sécherzestellen datt all Ufuerderunge erfëllt sinn a potenziell Themen geléist ginn. Regelméisseg iwwerpréift an iteréiert Designen fir Feedback a Verbesserungen ze integréieren.

7.Industrie Best Practices a Case Studien

7.1 Erfollegräich Fäll vu 16-Schicht PCB Design:

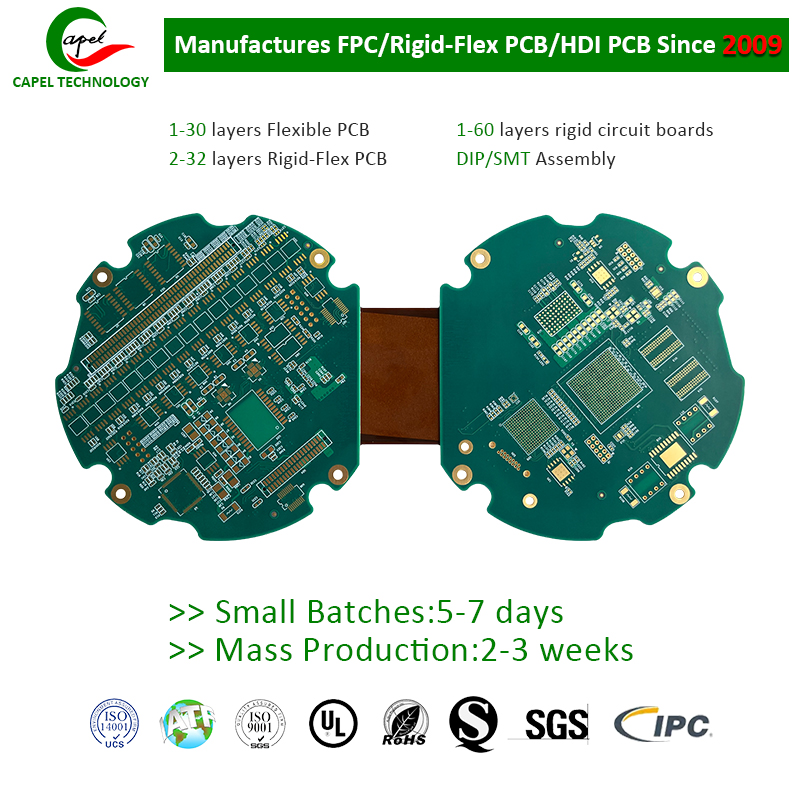

Fallstudie 1:Shenzhen Capel Technology Co., Ltd. entworf erfollegräich eng 16-Layer PCB fir Héich-Vitesse Reseau Equipement. Andeems se suergfälteg d'Signalintegritéit an d'Kraaftverdeelung berücksichtegen, erreechen se eng super Leeschtung an minimiséieren elektromagnetesch Interferenz. De Schlëssel fir hiren Erfolleg ass e komplett optimiséierte Stack-up Design mat kontrolléierter Impedanz Routing Technologie.

Fallstudie 2:Shenzhen Capel Technology Co., Ltd. entworf e 16-Schicht PCB fir e komplexe medizinescht Apparat. Andeems Dir eng Kombinatioun vun Uewerflächemontage an duerch-Lach Komponenten benotzt, hunn se e kompakten awer mächtegen Design erreecht. Virsiichteg Komponentplacement an effizient Routing garantéieren eng exzellente Signalintegritéit an Zouverlässegkeet.

7.2 Léiert vu Feeler a vermeit Falen:

Fallstudie 1:Puer PCB Hiersteller begéint Signal Integritéit Problemer am 16-Layer PCB Design vun Kommunikatioun Equipement. D'Grënn fir Versoen waren net genuch Berücksichtegung vun der Impedanzkontrolle a Mangel u korrekt Buedemplangverdeelung. D'Lektioun geléiert ass d'Signalintegritéitsufuerderunge virsiichteg ze analyséieren a strikt Impedanzkontroll Design Richtlinnen ëmzesetzen.

Fallstudie 2:E puer PCB Hiersteller hunn d'Fabrikatiounsfuerderunge mat sengem 16-Schicht PCB konfrontéiert wéinst der Komplexitéit vum Design. D'Iwwerbenotzung vu blann Vias an dicht gepackte Komponenten féiert zu Fabrikatiouns- a Montageschwieregkeeten. D'Lektioun geléiert ass e Gläichgewiicht tëscht Designkomplexitéit a Fabrikatiounsméiglechkeet ze treffen, mat de Fäegkeeten vum gewielte PCB Hiersteller.

Fir Falen a Fallen am 16-Schicht PCB Design ze vermeiden, ass et entscheedend fir:

a.Grëndlech verstoen d'Ufuerderunge an Aschränkungen vum Design.

b.Stacked Konfiguratiounen déi Signalintegritéit a Kraaftverdeelung optimiséieren. c.Verdeelt a arrangéiert Komponenten virsiichteg fir d'Performance ze optimiséieren an d'Fabrikatioun ze vereinfachen.

d.Ensure richteg Routing Techniken, wéi Kontroll Impedanz an exzessiv Notzung vun blann vias vermeiden.

e.Kollaboréieren a kommunizéieren effektiv mat allen Akteuren déi am Designprozess involvéiert sinn, dorënner elektresch a mechanesch Ingenieuren a Fabrikatiounsteams.

f.Perform iwwergräifend Design Verifizéierung a Simulatioun fir potenziell Themen z'identifizéieren an ze korrigéieren virun der Fabrikatioun.

Post Zäit: Sep-26-2023

Zréck